Data sheet acquired from Harris Semiconductor SCHS099B – Revised January 2003

# CMOS Quad Low-to-High Voltage Level Shifter Fee

#### High-Voltage Types (20-Volt Rating)

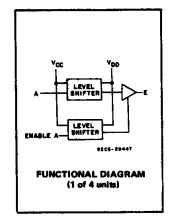

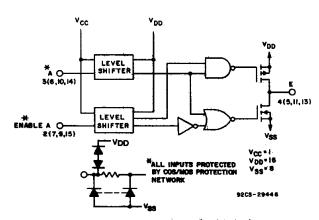

■ CD401098 contains four low-to-high-voltage level-shifting circuits. Each circuit will shift a low-voltage digital-logic input signal (A, B, C, D) with logical 1 = V<sub>CC</sub> and logical 0 = V<sub>SS</sub> to a higher-voltage output signal (E, F, G, H) with logical 1 = V<sub>DD</sub> and logical 0 = V<sub>SS</sub>.

The CD40109, unlike other low-to-high level-shifting circuits, does not require the presence of the high-voltage supply (VDD) before the application of either the low-voltage supply (V<sub>CC</sub>) or the input signals. There are no restrictions on the sequence of application of VDD, VCC, or the input signals. In addition, with one exception there are no restrictions on the relative magnitudes of the supply voltages or input signals within the device maximum ratings, provided that the input signal swings between VSS and at least 0.7 VCC;  $V_{CC}$  may exceed  $V_{DD}$ , and input signals may exceed  $V_{CC}$  and  $V_{DD}$ . When operated in the mode  $V_{CC} > V_{DD}$ , the CD40109 will operate as a high-to-low level-shifter.

The CD40109 also features individual threestate output capability. A low level on any of the separately enabled three-state output controls produces a high-impedance-state in the corresponding output.

The CD40109B-Series types are supplied in 16-lead ceramic dual-in-line packages (F3A suffix), 16-lead dual-in-line plastic packages (E suffix), 16-lead small-outline packages (NSR suffix), and 16-lead thin shrink small-outline packages (PW and PWR suffixes).

#### Applications:

- High-or-low level-shifting with three-state outputs for unidirectional or bidirectional bussing

- Isolation of logic subsystems using separate power supplies from supply sequencing, supply loss and supply regulation considerations

#### Features:

- Independence of power supply sequence considerations—V<sub>CC</sub> can exceed V<sub>DD</sub>, input signals can exceed both V<sub>CC</sub> and V<sub>DD</sub>

- Up and down level-shifting capability

- Three-state outputs with separate enable controls

- Standardized, symmetrical output characteristics

- 100% tested for quiescent current at 20 V

- Maximum input current of 1 μA at 18 V over full package-temperature range; 100 nA at 18 V and 25°C

- Noise margin (full package-temperature range)

- = 1 V at  $V_{CC}$  = 5 V,  $V_{DD}$  = 10 V

- = 2 V at V<sub>CC</sub> = 10 V, V<sub>DD</sub> = 15 V

- 5-V, 10-V, and 15-V parametric ratings

- Meets all requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of "B" Series CMOS Devices"

CD40109B Types

#### RECOMMENDED OPERATING CONDITIONS

For maximum reliability, nominal operating conditions should be selected so that operation is always within the following ranges:

| CHARACTERISTIC                  | LII  | 1 14 11 74 |       |

|---------------------------------|------|------------|-------|

|                                 | MIN. | MAX.       | UNITS |

| Supply-Voltage Range (For TA =  |      |            |       |

| Full Package-Temperature Range) | 3    | 18         | V     |

#### MAXIMUM RATINGS, Absolute-Maximum Values:

| DC SUPPLY-VOLTAGE RANGE, (VDD)                                             |

|----------------------------------------------------------------------------|

| Voltages referenced to VSS Terminal)0.5V to +20V                           |

| OUTPUT VOLTAGE RANGE, ALL OUTPUTS0.5 V to V <sub>DD</sub> +0.5 V           |

| DC INPUT CURRENT, ANY ONE INPUT ±10mA                                      |

| POWER DISSIPATION PER PACKAGE (PD):                                        |

| For T <sub>A</sub> = -55°C to +100°C                                       |

| For T <sub>A</sub> = +100°C to +125°C Derate Linearity at 12mW/°C to 200mW |

| DEVICE DISSIPATION PER OUTPUT TRANSISTOR                                   |

| FOR TA = FULL PACKAGE-TEMPERATURE RANGE (All Package Types) 100mW          |

| OPERATING-TEMPERATURE RANGE (TA)55°C to +125°C                             |

| STORAGE TEMPERATURE RANGE (Tatg)65°C to +150°C                             |

| LEAD TEMPERATURE (DURING SOLDERING):                                       |

At distance 1/16 ± 1/32 inch (1.59 ± 0.79mm) from case for 10s max . . . . . . . . . . . . +265°C

| and the second s |                      |            |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------|--|--|

| INF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | INPUTS               |            |  |  |

| A, B, C, D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ENABLE<br>A, B, C, D | E, F, G, H |  |  |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                    | 0          |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                    | 1          |  |  |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                    | Z          |  |  |

LOGIC 0 - LOW(V<sub>SS</sub>) X - DON'T CARE Z - HIGH IMPEDANCE LOGIC 1 - V<sub>CC</sub> at INPUTS and V<sub>DD</sub> at OUTPUTS

Fig.1 — CD40109B logic diagram (1 of 4 units).

### STATIC ELECTRICAL CHARACTERISTICS

| CHARACTER                                      | CONDITIONS |            |                        | LIMITS AT INDICATED TER |       |       |       | MPERATURES (°C) |                             |      | UNITS |

|------------------------------------------------|------------|------------|------------------------|-------------------------|-------|-------|-------|-----------------|-----------------------------|------|-------|

| ISTIC                                          | Vo<br>(V)  | VIN<br>(V) | V <sub>DD</sub><br>(V) | -55                     | -40   | +85   | +125  | Min.            | +25<br>Typ.                 | Max. |       |

| Quiescent Device<br>Current,                   | _          | 0,5        | 5                      | 1                       | 1     | 30    | 30    |                 | 0.02                        | 1    | μА    |

|                                                | - 1        | 0,10       | 10                     | 2                       | 2     | 60    | 60    |                 | 0.02                        | 2    |       |

| IDD Max.                                       | - 1        | 0,15       | 15                     | 4                       | - 4   | 120   | 120   | -               | 0.02                        | 4    | μΑ.   |

|                                                | _          | 0,20       | 20                     | 20                      | 20    | 600 . | 600   | <del></del>     | 0.04                        | 20   |       |

| Output Low                                     | 0.4        | 0,5        | 5                      | 0.64                    | 0.61  | 0.42  | 0.36  | 0.51            | 1                           |      |       |

| (Sink) Current                                 | 0.5        | 0,10       | 10                     | 1.6                     | 1.5   | 1.1   | 0.9   | 1.3             | 2.6                         |      | 100   |

| IOL Min.                                       | 1.5        | 0,15       | 15                     | 4.2                     | 4     | 2.8   | 2.4   | 3 4             | 6.8                         |      |       |

| Output High                                    | 4.6        | .0,5       | 5 .                    | -0.64                   | -0.61 | -0.42 | -0.36 | -0.51           | -1                          | -    | mA    |

| (Source)                                       | 2.5        | 0,5        | 5                      | -2                      | -1.8  | -1.3  | -1.15 | -1.6            | <sub>ှ</sub> -3.2           | -    |       |

| Current,                                       | 9.5        | 0,10       | 10                     | -1.6                    | -1.5  | -1.1  | -0.9  | -1.3            | -2.6                        | -    |       |

| IOH Min.                                       | 13.5       | 0,15       | 15                     | -4.2                    | -4    | -2.8  | 2.4   | -3.4            | -6.8                        | . –  |       |

| Output Voltage:                                | _          | 0,5        | 5                      | 0.05                    |       |       |       | _               | 0                           | 0.05 |       |

| Low-Level,                                     | _          | 0,10       | 10                     | 0.05                    |       |       |       | _               | 0                           | 0.05 |       |

| VOL Max.                                       |            | 0,15       | 15                     |                         | 0     | .05   |       | <u> </u>        | 0                           | 0.05 | V     |

| Output Voltage:                                |            | 0,5        | 5                      |                         | 4     | 95    |       | 4.95            | . 5                         | -    |       |

| High-Level,                                    | · -        | 0,10       | 10                     | 9.95                    |       |       |       | 9.95            | 10                          |      |       |

| VOH Min.                                       |            | 0,15       | 15                     |                         | 14    | :95   |       | 14.95           | 15                          | _    | 1 :   |

| Input Current IIN Max.                         |            | 0,18       | 18                     | ±0.1                    | ±0.1  | ±1    | ±1    | _               | ±10-5                       | ±0.1 | μΑ    |

| 3-State Output<br>Leakage Current<br>IOUT Max. |            | 0,18       | 18                     | ±0.4                    | ±0.4  | ±12   | ±12   | : 2.73<br>—     | ±10 <sup>-4</sup>           | ±0.4 | μΑ    |

|                                                | 35         | Vcc<br>(V) | V <sub>DD</sub><br>(V) | :                       |       | y 1   |       | n i e           |                             |      |       |

| Input Low<br>Voltage,                          | 1,9        | 5          | 10                     |                         |       | .5    |       |                 | _                           | 1.5  |       |

| VIL Max.                                       | 1.5, 13.5  | 10         | 15                     |                         |       | 3     |       | _               | _                           | 3    |       |

| Input High                                     | 1,9        | 5          | 10                     |                         |       | 3.5   | ,     | 3.5             |                             | -    | \ \   |

| Voltage,<br>VIH Min.                           | 1.5,13.5   | 10         | 15                     |                         |       | 7<br> |       | 7               | 19 <u>14 </u><br>19 1 4 1 1 | _    |       |

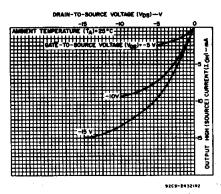

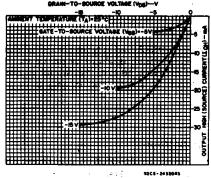

Fig.5 - Minimum output high (source)current characteristics.

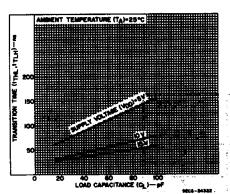

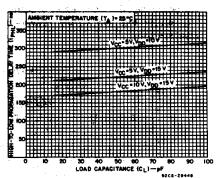

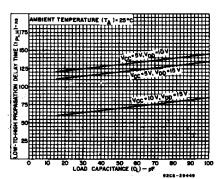

Fig.6 — Typical transition time as a function of load capacitance.

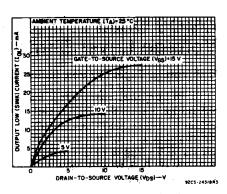

Fig.2 - Typical output low (sink) current characteristics.

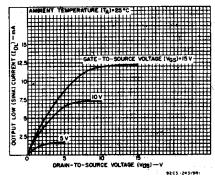

Fig.3 – Minimum output low (sink) current characteristics.

Fig.4 - Typical output high (source).

Fig.7 - Typical high-to-low propagation delay time as a function of load capacitance.

## CD40109B Types

# DYNAMIC ELECTRICAL CHARACTERISTICS at T $_A$ = 25°C, Input t $_r$ , t $_f$ = 20 ns, C $_L$ = 50 pF, R $_L$ = 200 k $\Omega$ unless otherwise specified

|                                | SHIFTING                              | Vcc      | V <sub>DD</sub> | 1.1M       | LIMITS     |       |

|--------------------------------|---------------------------------------|----------|-----------------|------------|------------|-------|

| CHARACTERISTIC                 | MODE                                  | (V)      | (V)             | Тур.       | Max.       | UNITS |

| Propagation Delay - Data Input | -                                     | 5        | 10              | 300        | 600        |       |

| to Output:                     | L-H                                   | 5        | 15              | 220        | 440        | ns    |

| Mah sa Laur Laur La            |                                       | 10       | 15              | 180        | 360        |       |

| High-to-Low Level, tpHL        |                                       | 10       | 5               | 250        | 500        |       |

|                                | H_L                                   | 15       | 5               | 250        | 500        |       |

|                                |                                       | 15       | 10              | 120        | 240        |       |

|                                | L–H                                   | 5        | 10              | 130        | 260        |       |

|                                |                                       | 5        | 15              | 120        | 240        |       |

| Low-to-High Level, tpLH        |                                       | 10       | 15              | 70         | 140        |       |

| Edw-to-riigh cever, tPLH       |                                       | 10       | 5               | 230        | 460        | ns    |

|                                | H-L                                   | 15       | 5               | 230        | 460        |       |

|                                |                                       | 15       | 10              | 80         | 160        |       |

| 3-State Disable Delay:         |                                       | 5        | 10              | 60         | 120        |       |

| R <sub>L</sub> = 1 kΩ          | L-H                                   | 5        | 15              | 75         | 150        |       |

| Output High to High            |                                       | 10       | 15              | 35         | 70         | ns    |

| Impedance, tpHZ                |                                       | 10       | 5               | 200        | 400        | 115   |

|                                | H-L                                   | 15       | 5               | 200        | 400        |       |

|                                |                                       | 15       | 10              | 40         | 80         |       |

| ·                              |                                       | 5        | 10              | 370        | 740        | ns    |

| Output Low to High             | L-H                                   | 5        | 15              | 300        | 600        |       |

| Impedance, tp_Z                |                                       | 10       | 15              | 250        | 500        |       |

| #                              |                                       | 10       | 5               | 250        | 500        |       |

| :                              | H-L                                   | 15       | 5               | 250        | 500        |       |

|                                |                                       | 15       | 10              | 130        | 260        |       |

| ,                              |                                       | 5        | 10              | 320        | 640        |       |

| High Impedance to              | L–H                                   | 5        | 15              | 230        | 460        |       |

| Output High, tpZH              | · · · · · · · · · · · · · · · · · · · | 10       | 15              | 180        | 360        | ns    |

|                                | H-L                                   | 10       | 5               | 300        | 600        |       |

|                                |                                       | 15<br>15 | 5<br>10         | 300<br>130 | 600<br>260 |       |

|                                |                                       | 5        | 10              |            |            |       |

|                                | L-H                                   | 5<br>5   | 15              | 100<br>80  | 200<br>160 |       |

| High Impedance to              |                                       | 10       | 15              | 40         | 80         |       |

| Output Low, tpZL               |                                       | 10       | 5               | 200        | 400        | ns    |

|                                | H-L                                   | 15       | 5               | 200        | 400        |       |

|                                | "-"                                   | 15       | 10              | 40         | 80         |       |

| 7 Turkeya (199 <b>-1994)</b>   | 要学生                                   | • 25·    | ¥ 10            | 50         | 100        | -     |

| Transition Time, TTHL, TTLH    | L-H                                   | 1 5      | 15              | 40         | 80         |       |

|                                |                                       | 10.      | 15              | 40         | 80         |       |

|                                | 1.4                                   | 10 🐗     | 5               | 100        | 200        | ns    |

|                                | H-L                                   | 15       | - 5             | 100        | 200        |       |

|                                |                                       | 15       | 10              | 50         | 100        |       |

| Input Capacitance, C           |                                       | Any      | Input           | 5          | 7.5        | ρF    |

|                                | IT.                                   | 14       |                 | L          |            |       |

Fig.8 — Typical low-to-high propagation delay time as a function of load capacitance.

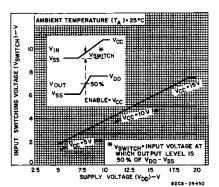

Fig.9 — Typical input switching as a function of high-level supply voltage.

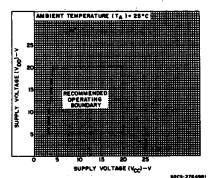

Fig. 10 — High-level supply voltage vs. low-level supply voltage.

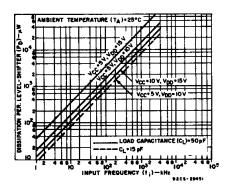

Fig.11 — Typical dynamic power dissipation as a function of input frequency.

# CD40109B Types

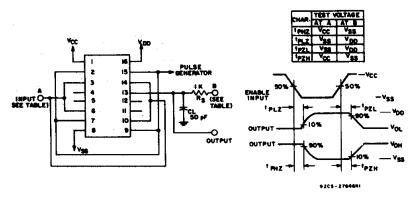

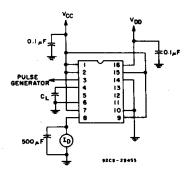

#### **TEST CIRCUITS**

Fig. 12 - Output enable delay times test circuit and waveforms.

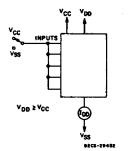

Fig. 13 - Quiescent device current.

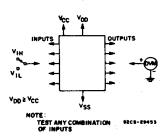

Fig. 14 - Input voltage.

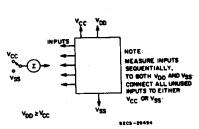

Fig. 15 - input current.

Fig. 16 - Dynamic power dissipation test circuit.

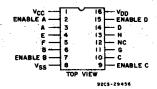

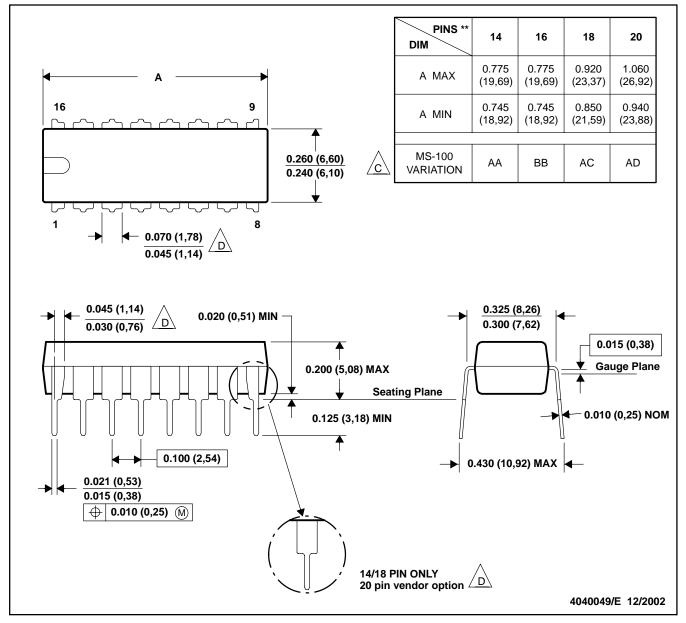

#### CD40109B TERMINAL ASSIGNMENT

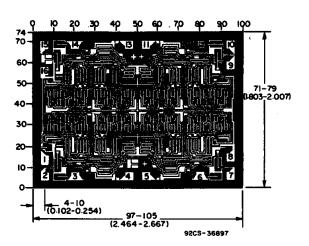

Dimensions in parentheses are in millimeters and are derived from the basic inch dimensions as indicated. Grid graduations are in mils ( $10^{-3}$  inch).

Dimensions and pad layout for CD401098H.

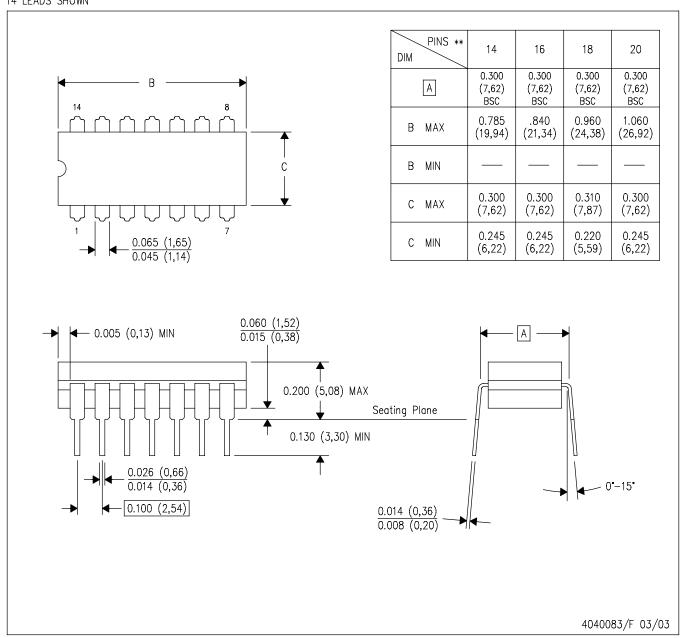

# 14 LEADS SHOWN

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package is hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only on press ceramic glass frit seal only.

- E. Falls within MIL STD 1835 GDIP1-T14, GDIP1-T16, GDIP1-T18 and GDIP1-T20.

### N (R-PDIP-T\*\*)

## 16 PINS SHOWN

### PLASTIC DUAL-IN-LINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

Falls within JEDEC MS-001, except 18 and 20 pin minimum body Irngth (Dim A).

The 20 pin end lead shoulder width is a vendor option, either half or full width.

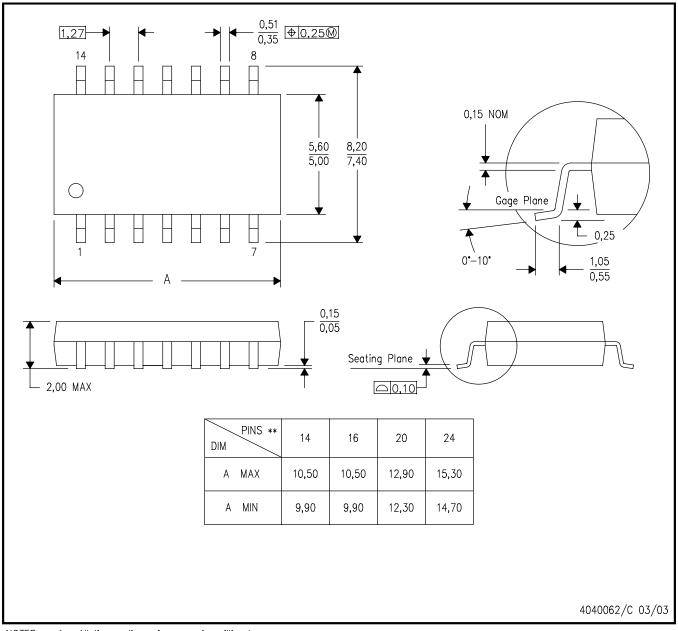

# **MECHANICAL DATA**

# NS (R-PDSO-G\*\*)

# 14-PINS SHOWN

### PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- . All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion, not to exceed 0,15.

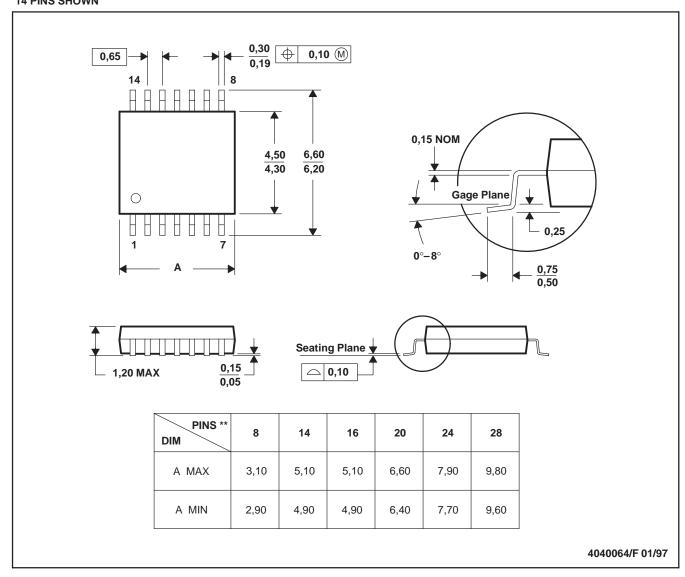

# PW (R-PDSO-G\*\*)

### 14 PINS SHOWN

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated