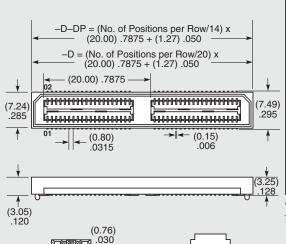

(0.80 mm) .0315"

**QSE SERIES**

# **HIGH-SPEED GROUND PLANE SOCKET**

#### **SPECIFICATIONS**

For complete specifications and recommended PCB layouts see www.samtec.com?QSE

Insulator Material: Liquid Crystal Polymer Terminal Material:

Phosphor Bronze

Plating: Au or Sn over 50 μ" (1.27 μm) Ni **Current Rating:**

Contacts: 2 A per pin (2 pins powered) Ground Plane: 23 A per ground plane

(1 ground plane powered)

Operating Temp Range:

-55 °C to +125 °C

Voltage Rating:

225 VAC (5 mm Stack Height) Max Cycles:

**RoHS Compliant:**

### **PROCESSING**

Lead-Free Solderable:

SMT Lead Coplanarity: (0.10 mm) .004" max (020-060) Board Stacking:

For applications requiring more than two connectors per board contact ipg@samtec.com

## RECOGNITIONS

For complete scope of recognitions see www.samtec.com/quality

### ALSO AVAILABLE (MOQ Required)

- 15 mm, 22 mm and 30 mm stack height

- 30 µ" (0.76 µm) Gold (Specify -H plating for Data Rate cable mating applications.)

- · Edge Mount

- 56 (-DP), 80, 100 positions per row

- · Retention, Guide Posts and Friction Lock options.

Some lengths, styles and options are non-standard, non-returnable.

**Board Mates:**

**Cable Mates:**

EQCD, EQDF (See Also Available Note)

Standoffs:

QSE

#### POWER/SIGNAL **APPLICATION**

Compatible with UMPT/UMPS for flexible two-piece power/signal solutions

(0.89)

035

Integral metal plane for power or ground Blade & Beam Design HIGH-SPEED CHANNEL PERFORMANCE QSE-D/QTE-D QSE-DP/QTE-DP

QTE-D/QSE-D or QTE-DP/QSE-DP @ 5 mm Mated Stack Height

Rating based on Samtec reference channel.For full SI performance data visit Samtec.comor contact SIG@samtec.com

01

**PLATING**

**OPTION**

**OTHER OPTION**

-020, -040, -060(40 total pins per bank = -D)

**PINS PER ROW**

NO. OF PAIRS

-014, -028, -042(14 pairs per bank = -D-DP)

\_F = Gold Flash on Signal Pins and Ground Plane, Matte Tin on tails

= 10 µ" (0.25 µm) Gold on Signal Pins and Ground Plane, Matte Tin on tails

-C\*

= Electro-Polished Selective 50 μ" (1.27 μm) min Au over 150 μ" (3.81 µm) Ni on Signal Pins in contact area. 10 μ" (0.25 μm) min Au over 50 μ" (1.27 μm) Ni on Ground Plane in contact area. Matte Tin over 50 μ" (1.27 µm) min Ni on all solder tails

C Plating passes

year MFG testing

= Single-Ended D-DP = Differential Pair (-01 only)

# -GP

= Guide Post (-020 only)

## –K

(8.25 mm) .325' DIA Polyimide Film Pick & Place Pad

## –TR

= Tape & Reel Packaging

Latching Option (N/A on -042 & -060 positions)

| QTE<br>LEAD STYLE | MATED HEIGHT<br>WITH QSE* |

|-------------------|---------------------------|

| -01               | (5.00) .197               |

| -02               | (8.00) .315               |

| -03               | (11.00) .433              |

| -04               | (16.00) .630              |

| -05               | (19.00) .748              |

| -07               | (25.00) .984              |

| -09               | (14.00) .551              |

|                   |                           |

Processing conditions will affect mated height. See SO Series for board space tolerances

(0.64)

.025