# MIC47050

# 500 mA ULDO with Low Input and Low Output Voltage

#### **Features**

- · Voltage Range

- Input Voltage: 1.0V to 3.6VBias Voltage: 2.3V to 5.5V

- · 0.4V to 2.0V Output Voltage Range

- · Low Dropout Voltage of 44 mV at 500 mA

- ±1.5% Initial Output Voltage Accuracy

- · High Bandwidth, Very Fast Transient Response

- Stable with a 1 µF Ceramic Output Capacitor

- · Logic Level Enable Input

- · UVLO on both Supply Voltages

- Available in Thermally Enhanced 2 mm x 2 mm DFN and TDFN Packages

- -40°C to +125°C Junction Temperature Range

- AEC-Q100 Qualified and PPAP Capable Available for DFN Package Only

#### **Applications**

- · Point-of-Load Applications

- · PDAs, Notebooks, and Desktops

- · Datacom and Telecom Systems

- · DSP, PLD and FPGA Power Supply

- Low Voltage Post Regulation

# **General Description**

The MIC47050 is a high speed, ultra-low dropout (ULDO), dual supply NMOS regulator designed to take advantage of point-of-load applications that use multiple supply rails to generate a low voltage, high-current power supply. The MIC47050 can source 500 mA of output current while only requiring a 1  $\mu F$  ceramic output capacitor for stability. A 1.5% output voltage accuracy, low dropout voltage (44 mV @ 500 mA), and low ground current makes this device ideally suited for mobile and point-of-load applications.

The MIC47050 has an NMOS output stage that offers very low output impedance. The NMOS output stage makes for a unique ability to respond very quickly to sudden load changes such as that required by a microprocessor, DSP, or FPGA. The MIC47050 consumes little quiescent current and can be used for driving the core voltages of mobile processors, post regulating a core DC/DC converter in any processor.

The MIC47050 is available in fixed and adjustable output voltages in a tiny 2 mm x 2 mm DFN and TDFN packages with an operating junction temperature range of –40°C to +125°C.

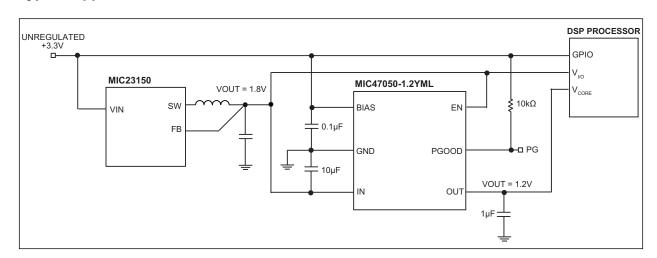

# **Typical Application Circuit**

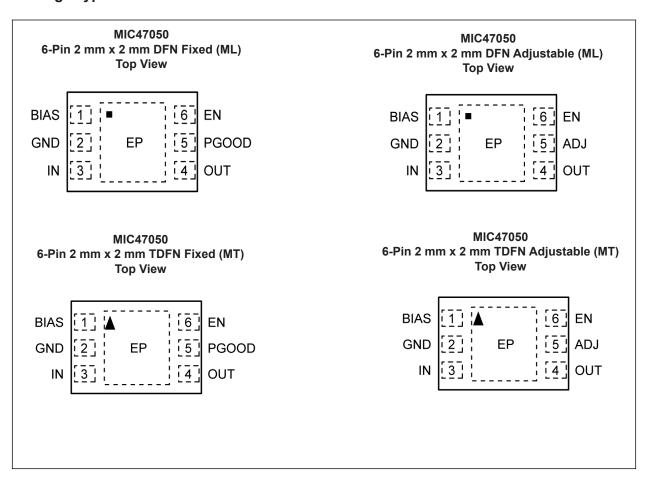

# **Package Types**

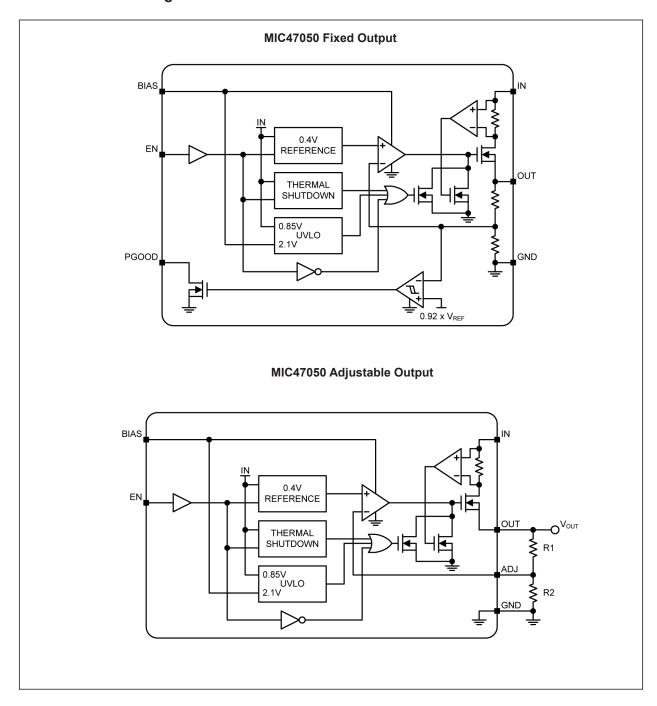

# **Functional Block Diagrams**

#### 1.0 ELECTRICAL CHARACTERISTICS

# Absolute Maximum Ratings †

| IN Supply Voltage (V <sub>IN</sub> )—0.3V to +4     | V        |

|-----------------------------------------------------|----------|

| Bias Supply Voltage (V <sub>BIAS</sub> )—0.3V to +6 | ١V       |

| Enable Voltage (V <sub>EN</sub> )—0.3V to +6        | ۷ć       |

| Power Good Voltage (V <sub>PGOOD</sub> )            |          |

| ADJ Pin Voltage (V <sub>AD,I</sub> )                | V        |

| OUT Pin Voltage (V <sub>OUT</sub> )                 | ,<br>INI |

| ESD Rating (Note 2)                                 |          |

# Operating Ratings ‡

| IN Supply Voltage (V <sub>IN</sub> )     | $+1.0V \text{ to } +3.6V (V_{IN} < V_{BIAS})$ |

|------------------------------------------|-----------------------------------------------|

| Bias Voltage (V <sub>BIAS</sub> )        |                                               |

| Enable Input Voltage (V <sub>EN</sub> )  |                                               |

| Power Good Voltage (V <sub>PGOOD</sub> ) |                                               |

| Output Voltage Range                     | 2                                             |

**† Notice:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability. Specifications are for packaged product only.

- **‡ Notice:** The device is not guaranteed to function outside its operating ratings.

- Note 1: The maximum allowable power dissipation of any  $T_A$  (ambient temperature) is  $P_{D(max)} = (T_{J(max)} T_A) / \theta_{JA}$ . Exceeding the maximum allowable power dissipation will result in excessive die temperature and the regulator will go into thermal shutdown.

- 2: Devices are ESD sensitive. Handling precautions are recommended. Human body model, 1.5 k $\Omega$  in series with 100 pF

# **ELECTRICAL CHARACTERISTICS**

Electrical Characteristics:  $V_{IN} = V_{OUT} + 0.5V$ ;  $V_{BIAS} = V_{OUT} + 2.1V$ ;  $C_{OUT} = 1 \mu F$ ;  $I_{OUT} = 100 \mu A$ ;  $T_J = +25^{\circ}C$ , **Bold** values indicate  $-40^{\circ}C \le T_J \le +125^{\circ}C$ ; unless otherwise noted. Specification for packaged product only.

| Parameter                                     | Symbol                               | Min. | Тур. | Max. | Units | Conditions                                                              |  |

|-----------------------------------------------|--------------------------------------|------|------|------|-------|-------------------------------------------------------------------------|--|

| Input Supply                                  |                                      |      |      |      |       |                                                                         |  |

| Input Voltage Range                           | V <sub>IN</sub>                      | 1.0  | _    | 3.6  | V     | _                                                                       |  |

| V <sub>IN</sub> UVLO Threshold (Note 1)       | V <sub>IN_UVLO</sub>                 | 0.7  | 0.85 | 1.0  | V     | V <sub>IN</sub> Rising                                                  |  |

| V <sub>IN</sub> UVLO Hysteresis (Note 2)      | V <sub>IN_UVLO_HYST</sub>            | _    | 40   | _    | mV    | _                                                                       |  |

| Ground Current in Shutdown                    | I <sub>GND</sub>                     | _    | 0.1  | 1.0  | μA    | V <sub>EN</sub> ≤ 0.2V (Regulator<br>Shutdown)                          |  |

| IN Bias Current                               | I <sub>IN</sub>                      | _    | 6    | 15   | μA    | I <sub>OUT</sub> = 500 mA; V <sub>IN</sub> = V <sub>OUT</sub><br>+ 0.5V |  |

| BIAS Supply                                   |                                      |      |      |      |       |                                                                         |  |

| BIAS Input Voltage                            | V <sub>BIAS</sub>                    | 2.3  | _    | 5.5  | V     | _                                                                       |  |

| V <sub>BIAS</sub> UVLO Threshold (Note 1)     | BIAS_UVLO                            | 1.7  | 2.1  | 2.3  | V     | V <sub>BIAS</sub> Rising                                                |  |

| V <sub>BIAS</sub> UVLO Hysteresis<br>(Note 2) | BIAS_UVLO_HYS                        | _    | 75   | _    | mV    | _                                                                       |  |

| Dropout Voltage                               | V <sub>BIAS</sub> - V <sub>OUT</sub> | _    | 1.15 | _    | V     | I <sub>OUT</sub> = 100 mA (Note 2)                                      |  |

| Dropout Voltage                               |                                      |      | 1.25 | 2.1  | V     | I <sub>OUT</sub> = 500 mA                                               |  |

| V <sub>BIAS</sub> Supply Current              | I <sub>BIAS</sub>                    | _    | 330  | 500  | μA    | $I_{OUT}$ = 1 mA; $V_{BIAS}$ = $V_{OUT}$ + 2.1V                         |  |

# **ELECTRICAL CHARACTERISTICS (CONTINUED)**

Electrical Characteristics:  $V_{IN} = V_{OUT} + 0.5V$ ;  $V_{BIAS} = V_{OUT} + 2.1V$ ;  $C_{OUT} = 1~\mu\text{F}$ ;  $I_{OUT} = 100~\mu\text{A}$ ;  $T_{J} = +25^{\circ}\text{C}$ , Bold values indicate  $-40^{\circ}\text{C} \le T_{J} \le +125^{\circ}\text{C}$ ; unless otherwise noted. Specification for packaged product only.

| Parameter                                                         | Symbol                                               |       | Тур.  | Max. | Units | Conditions                                      |  |  |

|-------------------------------------------------------------------|------------------------------------------------------|-------|-------|------|-------|-------------------------------------------------|--|--|

| V <sub>BIAS</sub> Supply Current in Shutdown (I <sub>BIAS</sub> ) | I <sub>BIAS_SHDN</sub>                               | _     | 0.1   | 1.0  | μA    | V <sub>EN</sub> ≤ 0.2V (Regulator<br>Shutdown)  |  |  |

| Output Voltage                                                    |                                                      |       |       |      |       |                                                 |  |  |

| Dropout Voltage                                                   | ., .,                                                | _     | 9     | 50   | mV    | I <sub>OUT</sub> = 100 mA                       |  |  |

| Diopout voitage                                                   | V <sub>IN</sub> - V <sub>OUT</sub>                   | _     | 44    | 120  | IIIV  | I <sub>OUT</sub> = 500 mA                       |  |  |

| Output Voltage Acquirecy                                          | V                                                    | -1.5  | _     | +1.5 | %     | I <sub>OUT</sub> = 100 μA, variation            |  |  |

| Output Voltage Accuracy                                           | V <sub>OUT</sub>                                     | -2.0  | _     | +2.0 | 70    | from nominal V <sub>OUT</sub>                   |  |  |

| V <sub>BIAS</sub> Line Regulation                                 | $\Delta V_{OUT}/$ $(V_{OUT} \times \Delta V_{BIAS})$ | -0.1  | 0.015 | 0.1  | %/V   | $V_{BIAS} = V_{OUT} + 2.1V \text{ to } 5.5V$    |  |  |

| V <sub>IN</sub> Line Regulation                                   | $\Delta V_{OUT}/$ $(V_{OUT} \times \Delta V_{IN})$   | -0.05 | 0.005 | 0.05 | %/V   | $V_{IN} = V_{OUT} + 0.5V \text{ to } 3.6V$      |  |  |

| Load Regulation                                                   | $\Delta V_{OUT}/V_{OUT}$                             | _     | 0.2   | 0.5  | %     | I <sub>OUT</sub> = 10 mA to 500 mA              |  |  |

| Current-Limit                                                     |                                                      |       |       |      |       |                                                 |  |  |

| Short-Circuit Current Limit                                       | I <sub>SC</sub>                                      | 0.6   | 1.6   | 3    | Α     | V <sub>IN</sub> = 2.7V;V <sub>OUT</sub> = 0V    |  |  |

| Enable Input                                                      |                                                      |       |       |      |       |                                                 |  |  |

| EN Logic Level High                                               | V <sub>EN_HIGH</sub>                                 | 1.0   | 0.77  | _    | V     | _                                               |  |  |

| EN Logic Level Low                                                | V <sub>EN_LOW</sub>                                  | _     | 0.67  | 0.2  | V     | _                                               |  |  |

| EN Hysteresis (Note 2)                                            | V <sub>EN_HYST</sub>                                 | _     | 100   | _    | mV    | _                                               |  |  |

| Enable Bias Current                                               | I <sub>EN_SHDN</sub>                                 | _     | 1     | 2    |       | V <sub>EN</sub> ≤ 0.2V (Regulator<br>Shutdown)  |  |  |

| Enable bias Current                                               | I <sub>EN</sub>                                      | _     | 6     | 10   | μA    | V <sub>EN</sub> = 1.0V (Regulator<br>Enabled)   |  |  |

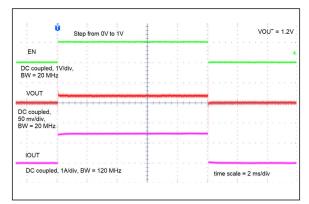

| Turn-On Time                                                      | t <sub>ON</sub>                                      | _     | 15    | 500  | μs    | $C_{OUT}$ = 1 $\mu$ F; 90% of typical $V_{OUT}$ |  |  |

| Thermal Protection                                                |                                                      |       |       |      |       |                                                 |  |  |

| Overtemperature Shutdown (Note 3)                                 | T <sub>SD</sub>                                      | _     | 160   | _    | °C    | T <sub>J</sub> Rising                           |  |  |

| Overtemperature Shutdown<br>Hysteresis (Note 3)                   | ΔT <sub>SD</sub>                                     | _     | 20    | _    | °C    | _                                               |  |  |

| Power Good                                                        |                                                      |       |       |      |       |                                                 |  |  |

| Power Good Threshold                                              | V <sub>PWRGD_TH_R</sub>                              | _     | 91    | 95   | %     | V <sub>OUT</sub> Rising                         |  |  |

| Voltage                                                           | V <sub>PWRGD_TH_F</sub>                              | 85    | 89    | _    | 70    | V <sub>OUT</sub> Falling                        |  |  |

| Power Good Hysteresis (Note 2)                                    | PWRGD <sub>HYST</sub>                                | _     | 2     | _    | %     | _                                               |  |  |

| Power Good Output Low<br>Voltage                                  | V <sub>PWRGD_L</sub>                                 | _     | 0.02  | 0.1  | V     | I <sub>PG</sub> = 250 μA                        |  |  |

| Power Good Leakage Current                                        | I <sub>PWRGD_L</sub>                                 | -1    | 0.01  | +1   | μA    | V <sub>PG</sub> = 5.0V                          |  |  |

# MIC47050

# **ELECTRICAL CHARACTERISTICS (CONTINUED)**

Electrical Characteristics:  $V_{IN} = V_{OUT} + 0.5V$ ;  $V_{BIAS} = V_{OUT} + 2.1V$ ;  $C_{OUT} = 1~\mu F$ ;  $I_{OUT} = 100~\mu A$ ;  $T_J = +25^{\circ}C$ , Bold values indicate  $-40^{\circ}C \le T_J \le +125^{\circ}C$ ; unless otherwise noted. Specification for packaged product only.

| Parameter                                  | Symbol          | Min.  | Тур.   | Max.  | Units             | Conditions                                                                |  |  |

|--------------------------------------------|-----------------|-------|--------|-------|-------------------|---------------------------------------------------------------------------|--|--|

| Reference Voltage (Adjustable Option Only) |                 |       |        |       |                   |                                                                           |  |  |

| 5 " I D ( ) V "                            | V <sub>FB</sub> | 0.394 | 0.4    | 0.406 | V                 | _ 100                                                                     |  |  |

| Feedback Reference Voltage                 |                 | 0.392 |        | 0.408 | V                 | I <sub>OUT</sub> = 100 μA                                                 |  |  |

| FB Bias Current (Note 2)                   | I <sub>FB</sub> | _     | 20     | _     | nA                | V <sub>FB</sub> = 0.8V                                                    |  |  |

| Output Voltage Noise and Ripple Rejection  |                 |       |        |       |                   |                                                                           |  |  |

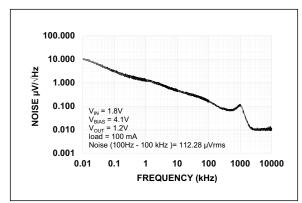

| Output Voltage Noise (Note 3)              | e <sub>N</sub>  |       | 122.71 | _     | μV <sub>RMS</sub> | $f$ = 10 Hz to 100 kHz; $I_{OUT}$ = 100 mA; $C_{OUT}$ = 1 μF              |  |  |

| Ripple Rejection (Note 3)                  | PSRR -          | _     | 50     | _     | - dB              | $f = 10 \text{ kHz}; C_{OUT} = 1.0 \mu\text{F}, I_{OUT} = 100 \text{ mA}$ |  |  |

| Tripple rejection (Note 3)                 |                 | _     | 37     | _     |                   | $f$ = 100 kHz; $C_{OUT}$ = 1.0 $\mu$ F, $I_{OUT}$ = 100 mA                |  |  |

<sup>1:</sup> Both V<sub>IN</sub> and V<sub>BIAS</sub> UVLO thresholds must be met for the output voltage to turn on. If either of the two input voltages is below the UVLO thresholds, the output is disabled.

<sup>2:</sup> These parameters are characterized but not production tested.

<sup>3:</sup> Design guidance only, not production tested.

# **TEMPERATURE SPECIFICATIONS (Note 1)**

| Parameters                  | Symbol         | Min. | Тур. | Max. | Units  | Conditions         |  |

|-----------------------------|----------------|------|------|------|--------|--------------------|--|

| Temperature Ranges          |                |      |      |      |        |                    |  |

| Lead Temperature            | _              | _    | _    | 260  | °C     | Soldering, 10 sec. |  |

| Storage Temperature Range   | T <sub>S</sub> | -65  | _    | +150 | °C     | _                  |  |

| Junction Temperature Range  | TJ             | -40  | _    | +125 | °C     | _                  |  |

| Package Thermal Resistances |                |      |      |      |        |                    |  |

| Thermal Resistance DFN-6    | $\theta_{JA}$  | _    | 90   | _    | °C/W   | _                  |  |

| Thermal Resistance DFN-0    | $\theta_{JC}$  | _    | 45   | _    | C/VV   | _                  |  |

| Thermal Desistance TDEN 6   | $\theta_{JA}$  | _    | 90   | _    | °C/W   | _                  |  |

| Thermal Resistance TDFN-6   | $\theta_{JC}$  | _    | 45   | _    | ] C/VV | _                  |  |

Note 1: The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction to air (i.e., T<sub>A</sub>, T<sub>J</sub>, θ<sub>JA</sub>). Exceeding the maximum allowable power dissipation will cause the device operating junction temperature to exceed the maximum +125°C rating. Sustained junction temperatures above +125°C can impact the device reliability.

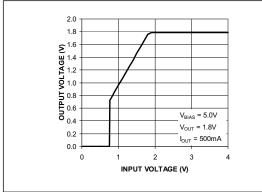

#### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

FIGURE 2-1: Output Voltage vs. Input Voltage.

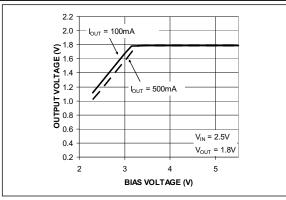

**FIGURE 2-4:** Output Voltage vs. Bias Voltage.

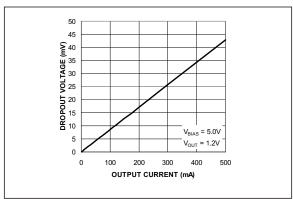

**FIGURE 2-2:** Input Dropout Voltage vs. Output Current.

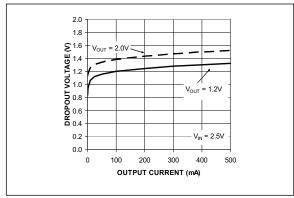

**FIGURE 2-5:** Bias Dropout Voltage vs. Output Current.

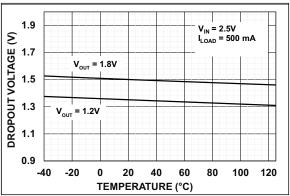

FIGURE 2-3: Input Dropout Voltage vs. Temperature.

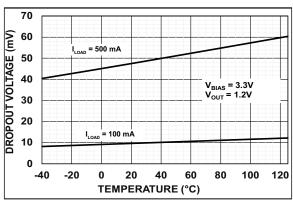

FIGURE 2-6: Bias Dropout Voltage vs. Temperature.

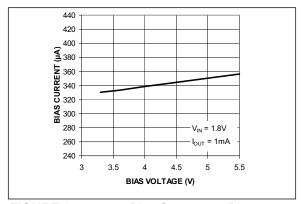

FIGURE 2-7: Voltage.

Bias Current vs. Bias

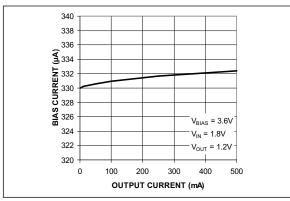

FIGURE 2-8:

Current.

Bias Current vs. Output

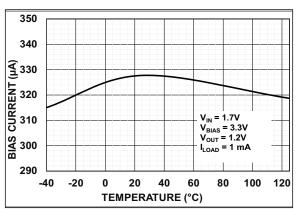

FIGURE 2-9: Temperature.

Bias Current vs.

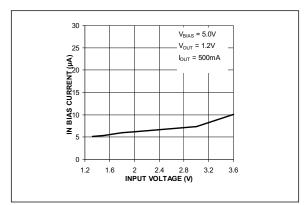

FIGURE 2-10: Voltage.

Input Bias Current vs. Input

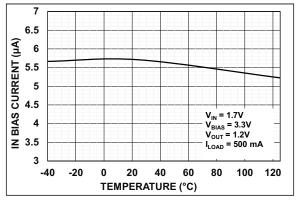

FIGURE 2-11: Temperature.

Input Bias Current vs.

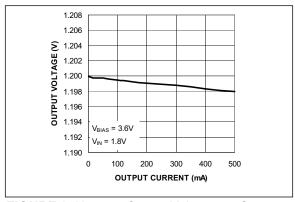

FIGURE 2-12: Current.

Output Voltage vs. Output

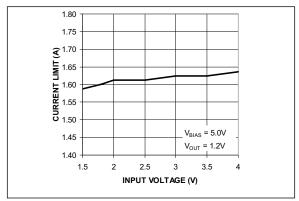

**FIGURE 2-13:** Current-Limit vs. Input Voltage.

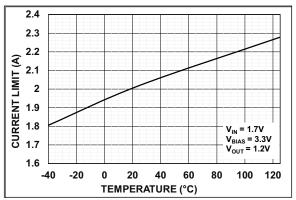

**FIGURE 2-14:** Current-Limit vs. Input Temperature.

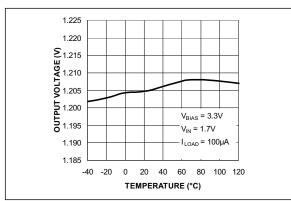

**FIGURE 2-15:** Output Voltage vs. Temperature.

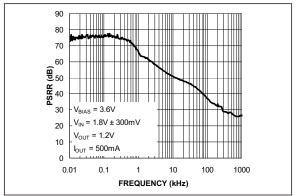

**FIGURE 2-16:** Power Supply Ripple Rejection (Input Voltage).

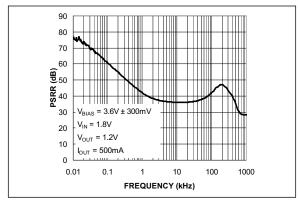

**FIGURE 2-17:** Power Supply Ripple Rejection (Bias Voltage).

FIGURE 2-18: Output Noise.

FIGURE 2-19: Enabled into Short-Circuit.

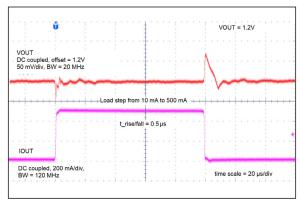

FIGURE 2-20: Load Transient Response.

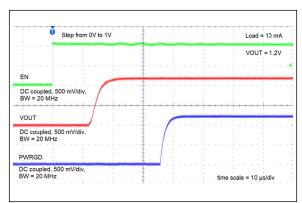

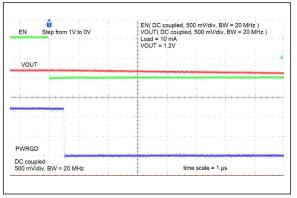

FIGURE 2-21: Enable Turn-On Time.

FIGURE 2-22: Enable Turn-Off Time.

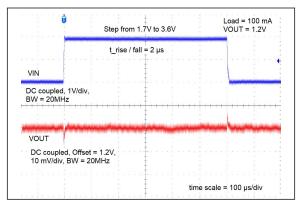

FIGURE 2-23: Input Line Transient.

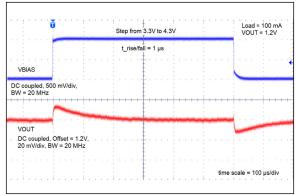

FIGURE 2-24: Bias Line Transient.

# 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| Pin Number (Fixed) | Pin Number<br>(Adjustable) | Pin Name | Description                                                                                                                                                                                                                                                                                                        |

|--------------------|----------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | 1                          | BIAS     | Bias Supply. The bias supply is the power supply for the internal circuitry of the regulator.                                                                                                                                                                                                                      |

| 2                  | 2                          | GND      | Ground. Ground pins and exposed pad must be connected externally.                                                                                                                                                                                                                                                  |

| 3                  | 3                          | IN       | Input Supply. Drain of NMOS pass transistor, which is the power input voltage for regulator. The NMOS pass transistor steps down this input voltage to create the output voltage.                                                                                                                                  |

| 4                  | 4                          | OUT      | Output. Output voltage of regulator.                                                                                                                                                                                                                                                                               |

| 5                  | _                          | PGOOD    | Power Good Output. Open-drain output. Output is driven low when the output voltage is less than the power good threshold of its programmed nominal output voltage. When the output goes above the power good threshold, the open-drain output goes high impedance, allowing it to be pulled up to a fixed voltage. |

| _                  | 5                          | ADJ      | Adjust Input. Connect external resistor divider to program the output voltage.                                                                                                                                                                                                                                     |

| 6                  | 6                          | EN       | Enable: TTL/CMOS compatible input. Logic-high = enable,<br>Logic-low = shutdown. Do not leave floating.                                                                                                                                                                                                            |

| ePAD               | ePAD                       | GND      | Exposed thermal pad. Connect to the ground plane to maximize thermal performance.                                                                                                                                                                                                                                  |

#### 4.0 FUNCTIONAL DESCRIPTION

The MIC47050 is a high speed, ultra-low dropout, dual supply NMOS ULDO designed to take advantage of point-of-load applications that use multiple supply rails to generate a low voltage, high-current power supply. The MIC47050 can source 0.5A of output current while only requiring a 1  $\mu F$  ceramic output capacitor for stability. The MIC47050 regulator is fully protected from damage due to fault conditions, offering linear current limiting and thermal shutdown.

# 4.1 Bias Supply Voltage

$V_{BIAS},$  requiring relatively light current, provides power to the control portion of the MIC47050. Bypassing on the bias pin is recommended to improve performance of the regulator during line and load transients. Small 0.1  $\mu F$  ceramic capacitors from  $V_{BIAS}$  to ground help reduce high frequency noise from being injected into the control circuitry from the bias rail and are good design practice.

#### 4.2 Input Supply Voltage

$V_{\text{IN}}$  provides the supply to power the LDO. The minimum input voltage is 1.0V. This allows conversion from low voltage supplies to reduce the power dissipation in the pass element.

#### 4.3 Input Capacitor

The MIC47050 is a high-performance, high bandwidth device. Therefore, it requires a well bypassed input supply for optimal performance. A 1  $\mu F$  capacitor is the minimum required for stability. A 10  $\mu F$  ceramic capacitor is recommended for most applications, especially if the LDO's headroom  $(V_{IN}-V_{OUT})$  is small and/or if large load transients are present. Fast load transient and low headroom requires a larger input filter capacitor to ensure that the regulator does not drop out of regulation. A 10  $\mu F$  will better attenuate any voltage glitches from exceeding the maximum voltage rating of the part.

Additional high frequency capacitors, such as small valued NPO dielectric type capacitors, help filter out high frequency noise and are good practice in any RF based circuit.

X7R and X5R dielectric ceramic capacitors are recommended because of their temperature performance. X7R type capacitors change capacitance by 15% over their operating temperature range and are the most stable type of ceramic capacitors. Z5U and Y5V dielectric capacitors are not recommended since they change value by as much as 50% and 60% respectively over their operating temperature ranges. To use a ceramic chip capacitor with Y5V dielectric, the

value must be much higher than an X7R ceramic or a tantalum capacitor to ensure the same capacitance value over the operating temperature range.

Tantalum capacitors have a very stable dielectric (10% over their operating temperature range) and can also be used with this device. See **Section 2.0 "Typical Performance Curves"** for examples of load transient response.

# 4.4 Output Capacitor

The MIC47050 requires an output capacitor of 1  $\mu F$  or greater to maintain stability. The design is optimized for use with low ESR ceramic chip capacitors. High ESR capacitors may cause high frequency oscillation. The output capacitor can be increased, but performance has been optimized for a 1  $\mu F$  ceramic output capacitor and does not improve significantly with larger capacitance.

The output capacitor type and placement criteria are the same as the input capacitor. See the **Section 4.3** "Input Capacitor" for a detailed description.

#### 4.5 Minimum Load Current

The MIC47050, unlike most other regulators, does not require a minimum load to maintain output voltage regulation.

# 4.6 Adjustable Regulator Design

The MIC47050 adjustable version allows programming the output voltage from 0.4V to 2.0V. Two external resistors are required. The R1 resistor value between  $V_{OUT}$  and the ADJ pin should not exceed 10  $k\Omega,$  as larger values can cause instability. R2 connects between the ADJ pin and ground. The resistor values are calculated as follows:

#### **EQUATION 4-1:**

$$R1 = R2\left(\frac{V_{OUT}}{V_{REE}} - 1\right)$$

Where:

V<sub>OUT</sub> = The desired output voltage V<sub>REF</sub> = The internal reference voltage

$V_{REF} = 0.4V$

#### 4.7 Enable/Shutdown

The MIC47050 comes with a single active-high enable pin that allows the regulator to be disabled. Forcing the enable pin low disables the regulator and sends it into a "zero" off mode current state. In this state, current

consumed by the regulator goes nearly to zero. Forcing the enable pin high enables the output voltage. The active-high enable pin uses CMOS technology and the enable pin cannot be left floating. A floating enable pin may cause an indeterminate state on the output.

# 4.8 Power Good (PGOOD)

The Power Good (PGOOD) pin is an open-drain output that goes low when the output voltage (fixed version) drops below the PGOOD threshold voltage.

The pull-up resistor value should be large enough to guarantee a proper low voltage when the PGOOD pin pulls low. The PGOOD low voltage is typically 0.1V at 250  $\mu A$  current. A 10  $k\Omega$  resistor or greater is recommended when pulling up to 3.3V bias.

If the PGOOD function is not required, the PGOOD pin may be left unconnected.

#### 4.9 Thermal Shutdown

The MIC47050 has an internal overtemperature protection feature. This feature is for protection only. The device should never be intentionally operated near this temperature as this may reduce long term reliability. The device will turn off when the overtemperature threshold is exceeded. A 20°C hysteresis is built in to allow the device to cool before turning back on.

#### 4.10 Thermal Considerations

The MIC47050 is designed to provide 0.5A of continuous current in a very small package. Maximum ambient operating temperature can be calculated based on the output current and the voltage drop across the part. Given that the input voltage is 1.8V, the output voltage is 1.2V and the output current is 0.5A. The actual power dissipation of the regulator circuit can be determined using Equation 4-2:

#### **EQUATION 4-2:**

$$\begin{split} P_D &= (V_{IN} - V_{OUT})I_{OUT} + V_{IN} \times I_{IN} + \\ V_{BIAS} \times I_{BIAS} \end{split}$$

Because this device is CMOS, the ground current is insignificant for power dissipation and can be ignored for this calculation.

#### **EQUATION 4-3:**

$$P_D = (1.8V - 1.2V) \times 0.5A = 0.3W$$

To determine the maximum ambient operating temperature of the package, use the junction-to-ambient thermal resistance of the device and the following basic equation:

#### **EQUATION 4-4:**

$$P_{D(MAX)} = \left[ \frac{T_{J(MAX)} - T_A}{\Theta_{JA}} \right]$$

Where:

$T_{J(MAX)}$  = 125°C, the maximum junction tempera-

ture of the die

$\theta_{JA}$  = 90°C/W, the thermal resistance

Table 4-1 shows junction-to-ambient thermal resistance for the MIC47050 in the DFN or TDFN packages.

TABLE 4-1: THERMAL RESISTANCE

| Package                   | θ <sub>JA</sub> Recommended<br>Min. Footprint | θЈС    |

|---------------------------|-----------------------------------------------|--------|

| 6-Pin 2 mm x 2 mm<br>DFN  | 90°C/W                                        | 45°C/W |

| 6-Pin 2 mm x 2 mm<br>TDFN | 90°C/W                                        | 45°C/W |

Substituting  $P_D$  for  $P_{D(max)}$  and solving for the ambient operating temperature will give the maximum operating conditions for the regulator circuit. The junction-to-ambient thermal resistance for the minimum footprint is 90°C/W. The maximum power dissipation must not be exceeded for proper operation. For example, when operating the MIC47050-1.2YML at an input voltage of 1.8V and a 0.5A load with a minimum footprint layout, the maximum ambient operating temperature  $T_A$  can be determined as follows:

#### **EQUATION 4-5:**

$$T_A = T_{J(MAX)} - \theta_{JA} \times P_{D(MAX)}$$

$$T_A = 125^{\circ}C - 90^{\circ}C/W \times 0.3W$$

$$T_A = 98^{\circ}C$$

Therefore, a 1.2V application with 0.5A of output current can accept an ambient operating temperature of 98°C in a 2 mm x 2 mm DFN or TDFN package.

#### 4.11 Thermal Measurements

Measuring the IC's case temperature is recommended to insure it is within its operating limits. Although this might seem like a very elementary task, it is easy to get erroneous results. The most common mistake is to use the standard thermal couple that comes with a thermal meter. This thermal couple wire gauge is large, typically 22 gauge, and behaves like a heat sink, resulting in a lower case measurement.

Two methods of temperature measurement are using a smaller thermal couple wire or an infrared thermometer. If a thermal couple wire is used, it must be constructed of 36 gauge wire or higher (smaller wire size) to minimize the wire heat sinking effect.

In addition, the thermal couple tip must be covered in either thermal grease or thermal glue to make sure that the thermal couple junction is making good contact with the case of the IC. Omega brand thermal couple (5SC-TT-K-36-36) is adequate for most applications.

Wherever possible, an infrared thermometer is recommended. The measurement spot size of most infrared thermometers is too large for an accurate reading on a small form factor ICs. However, a IR thermometer from Optris has a 1 mm spot size, which makes it a good choice for the 2 mm x 2 mm DFN or TDFN package. An optional stand makes it easy to hold the beam on the IC for long periods of time.

For a full discussion of heat sinking and thermal effects of voltage regulators, refer to the "Regulator Thermals" section of Designing with Low-Dropout Voltage Regulators handbook.

#### 5.0 PACKAGING INFORMATION

# 5.1 Package Marking Information

NNN

Legend: XX...XProduct code or customer-specific information Year code (last digit of calendar year) Year code (last 2 digits of calendar year) ΥY  $\mathsf{WW}$ Week code (week of January 1 is week '01') Alphanumeric traceability code NNN Pb-free JEDEC® designator for Matte Tin (Sn) (e3) This package is Pb-free. The Pb-free JEDEC designator (@3)) can be found on the outer packaging for this package. •, ▲, ▼ Pin one index is identified by a dot, delta up, or delta down (triangle mark).

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information. Package may or may not include the corporate logo.

Underbar (\_) and/or Overbar (¯) symbol may not be to scale.

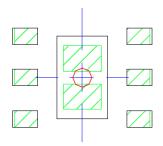

# 6-Lead 2 mm x 2 mm DFN Package Outline and Recommended Land Pattern

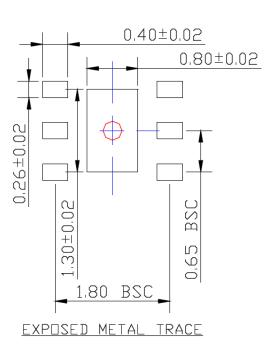

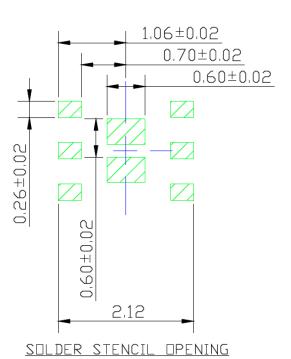

# TITLE 6 LEAD DFN 2x2mm PACKAGE OUTLINE & RECOMMENDED LAND PATTERN DRAWING # DFN22-6LD-PL-1 UNIT MM PIN #1 ID R0.100 TYP -2.00 BSC <del>-</del> - 0.35±0.05 0.25±0.05 1.40±0.05 1.55 REF 2.00 BSC 0.65 EXP. PAD BSC 0.80±0.05 EXP. PAD TOP VIEW BOTTOM VIEW NDTE: 1, 2, 3 NOTE: 1, 2, 3 0.850±0.050 -0,203±0,025 △ 0.05 C SEATING PLANE 0.000-0.050 END VIEW NOTE: 1, 2, 3 NOTE: 1. MAX PACKAGE WARPAGE IS 0.05 MM 2. MAX ALLOWABLE BURR IS 0.076MM IN ALL DIRECTIONS 3. PIN #1 IS ON TOP WILL BE LASER MARKED 4. RED CIRCLE IN LAND PATTERN INDICATE THERMAL VIA. SIZE SHOULD BE 0.30-0.3M IN DIAMETER AND SHOULD BE CONNECTED TO GND FOR MAX THERMAL PERFORMANCE 5. GREEN RECTANGLES (SHADED AREA) indicate SOLDER STENCIL OPENING ON EXPOSED PAD AREA. SIZE SHOULD BE 0.60×0.40 MM IN SIZE, 0.20 MM SPACING.

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging.

# POD-Land Pattern drawing # DFN22-6LD-PL-1

# RECOMMENDED LAND PATTERN NOTE: 4,5

STACKED-UP

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging.

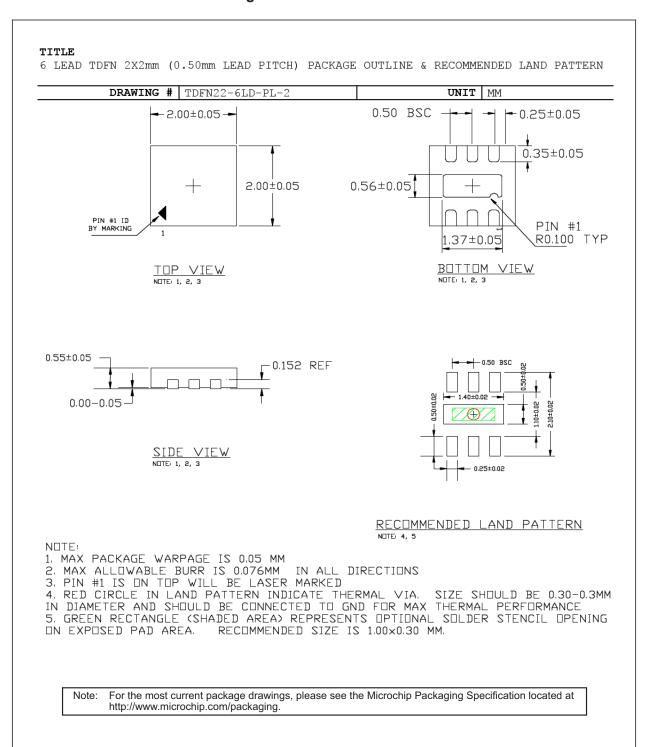

# 6-Lead 2 mm x 2 mm TDFN Package Outline and Recommended Land Pattern

NOTES:

# APPENDIX A: REVISION HISTORY

# Revision A (July 2018)

- Converted Micrel document MIC47050 to Microchip data sheet DS20006050C.

- Added Automotive feature AEC-Q100 Qualified and PPAP Capable in the Section "Features"

- Updated images for Figure 2-10, Figure 2-11, Figure 2-18, Figure 2-19 through Figure 2-24.

# **Revision B (September 2018)**

Updated images for Figure 2-3, Figure 2-6, Figure 2-9, Figure 2-11, Figure 2-14 and Figure 2-15.

# Revision C (February 2019)

• Added Note 2 and Note 3 to the Electrical table.

NOTES:

# PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, contact your local Microchip representative or sales office.

Device:

MIC47050: 500 mA ULDO with Low Input and Low

Output Voltage

Output Voltage:

Junction

Y = -40°C to +125°C, RoHS Compliant

Temperature Range:

Package: ML =

ML = 6-Lead 2 mm x 2 mm x 0.9 mm DFN MT = 6-Lead 2 mm x 2 mm x 0.5 mm TDFN

Media Type: TR = 5000/Reel

Examples:

a) MIC47050YML-TR:

500 mA ULDO with Low Input and Low Output Voltage, Adjustable Output Voltage, -40°C to +125°C Temperature Range, 6-Lead 2 mm x 2 mm x 0.9 mm DFN Package, 5000/

Reel

b) MIC47050-1.2YML-TR:

and Low Output Voltage, 1.2V Fixed Output Voltage, -40°C to +125°C Temperature Range, 6-Lead 2 mm x 2 mm x 0.9 mm DFN Package, 5000/

500 mA ULDO with Low Input

Reel

c) MIC47050-1.8YML-TR:

and Low Output Voltage, 1.8V Fixed Output Voltage, -40°C to +125°C Temperature Range, 6-Lead 2 mm x 2 mm x 0.9 mm DFN Package, 5000/

500 mA ULDO with Low Input

0.9 mm Reel

e) MIC47050YMT-TR:

500 mA ULDO with Low Input and Low Output Voltage, Adjustable Output Voltage, -40°C to +125°C Temperature Range, 6-Lead 2 mm x 2 mm x 0.5 mm TDFN Package, 5000/

Ree

f) MIC47050-1.2YMT-TR:

500 mA ULDO with Low Input and Low Output Voltage, 1.2V

Fixed Output Voltage,

-40°C to +125°C Temperature Range, 6-Lead 2 mm x 2 mm x 0.5 mm TDFN Package, 5000/

Reel

g) MIC47050-1.8YMT-TR: 500 mA ULDO with Low Input

and Low Output Voltage, 1.8V Fixed Output Voltage, -40°C to +125°C Temperature

Range, 6-Lead 2 mm x 2 mm x 0.5 mm TDFN Package, 5000/

Reel

Note 1:

Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the

Tape and Reel option.

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### **Trademarks**

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A. Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, memBrain, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM, net. PICkit, PICtail, PowerSmart, PureSilicon. QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2018, Microchip Technology Incorporated, All Rights Reserved. ISBN: 978-1-5224-4156-4

# Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/support

Web Address: www.microchip.com

**Atlanta** Duluth, GA

Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Fax: 317-773-5453 Tel: 317-536-2380 **Los Angeles** Mission Viejo, CA

Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

**Raleigh, NC** Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

China - Chengdu Tel: 86-28-8665-5511

China - Chongqing Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

**China - Nanjing** Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

**China - Shanghai** Tel: 86-21-3326-8000

**China - Shenyang** Tel: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

**China - Xian** Tel: 86-29-8833-7252

China - Xiamen

Tel: 86-592-2388138

**China - Zhuhai** Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

**Japan - Tokyo** Tel: 81-3-6880- 3770

Korea - Daegu Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

**Austria - Wels** Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-67-3636

**Germany - Karlsruhe** Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

**Poland - Warsaw** Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820