Data Sheet February 11, 2005 FN7049.1

### Differential Line Receiver

The EL2142 is a very high bandwidth amplifier designed to extract the difference signal from noisy environments, and is thus primarily targeted for applications such as receiving signals from twisted pair lines, or any application where common mode noise injection is likely to occur.

The EL2142 is stable for a gain of one, and requires two external resistors to set the voltage gain.

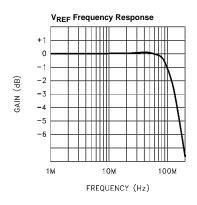

The output common mode level is set by the reference pin  $(V_{REF})$ , which has a -3dB bandwidth of over 100MHz. Generally, this pin is grounded, but it can be tied to any voltage reference.

The output can deliver a minimum of ±50mA and is short circuit protected to withstand a temporary overload condition.

## Ordering Information

| PART<br>NUMBER               | PACKAGE                 | TAPE &<br>REEL | PKG. DWG. # |

|------------------------------|-------------------------|----------------|-------------|

| EL2142CS                     | 8-pin SOIC              | -              | MDP0027     |

| EL2142CS-T7                  | 8-pin SOIC              | 7"             | MDP0027     |

| EL2142CS-T13                 | 8-pin SOIC              | 13"            | MDP0027     |

| EL2142CSZ<br>(See Note)      | 8-pin SOIC<br>(Pb-free) | -              | MDP0027     |

| EL2142CSZ-T7<br>(See Note)   | 8-pin SOIC<br>(Pb-free) | 7"             | MDP0027     |

| EL2142CSZ-<br>T13 (See Note) | 8-pin SOIC<br>(Pb-free) | 13"            | MDP0027     |

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### **Features**

- Differential input range ±2.3V

- · 150MHz 3dB bandwidth

- 400V/µs slewrate

- ±5V supplies or single supply

- 50mA minimum output current

- Output swing (100 $\Omega$  load) to within 1.5V of supplies

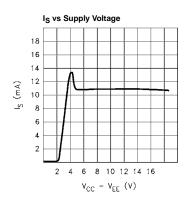

- Low power-11mA typical supply current

- · Pb-free available (RoHS compliant)

## **Applications**

- · Twisted pair receiver

- · Differential line receiver

- · VGA over twisted pair

- · ADSL/HDSL receiver

- · Differential to single ended amplification.

- · Reception of analog signals in a noisy environment.

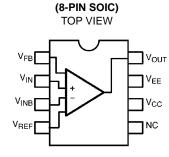

#### **Pinout**

EL2142

## **Absolute Maximum Ratings** (T<sub>A</sub> = 25°C)

| Supply Voltage (V <sub>CC</sub> –V <sub>EE</sub> ) | Operating Junction Temperature                |

|----------------------------------------------------|-----------------------------------------------|

| Maximum Output Current                             | Recommended Operating Temperature40°C to 85°C |

| Storage Temperature Range65°C to +150°C            |                                               |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

# **DC Electrical Specifications** $V_{CC} = +5V$ , $V_{EE} = -5V$ , $T_{EE} = 25^{\circ}C$ , $V_{IN} = 0V$ , $R_{L} = 100$ , unless otherwise specified

| PARAMETER              | DESCRIPTION                                                                 | MIN  | TYP  | MAX  | UNITS  |

|------------------------|-----------------------------------------------------------------------------|------|------|------|--------|

| V <sub>SUPPLY</sub>    | Supply Operating Range (V <sub>CC</sub> -V <sub>EE</sub> )                  | ±3.0 | ±5.0 | ±6.3 | V      |

| IS                     | Power Supply Current (no load)                                              |      | 11   | 14   | mA     |

| Vos                    | Input Referred Offset Voltage                                               | -25  | 10   | 40   | mV     |

| I <sub>IN</sub>        | Input Bias Current (V <sub>IN</sub> , V <sub>IN</sub> B, V <sub>REF</sub> ) | -20  | 6    | 20   | μΑ     |

| Z <sub>IN</sub>        | Differential Input Resistance                                               |      | 400  |      | kΩ     |

| C <sub>IN</sub>        | Differential Input Capacitance                                              |      | 1    |      | pF     |

| V <sub>DIFF</sub>      | Differential Input Range                                                    | ±2.0 | ±2.3 |      | V      |

| A <sub>VOL</sub>       | Open Loop Voltage Gain                                                      |      | 75   |      | dB     |

| V <sub>IN</sub>        | Input Common Mode Voltage Range                                             | -2.6 |      | +4.0 | V      |

| V <sub>OUT</sub>       | Output Voltage Swing (50Ω load to GND)                                      | ±2.9 | ±3.1 |      | V      |

| I <sub>OUT</sub> (min) | Minimum Output Current                                                      | 50   | 60   |      | mA     |

| V <sub>N</sub>         | Input Referred Voltage Noise                                                |      | 36   |      | nV/√Hz |

| V <sub>REF</sub>       | Output Voltage Control Range                                                | -2.5 |      | +3.3 | V      |

| PSRR                   | Power Supply Rejection Ratio                                                | 60   | 70   |      | dB     |

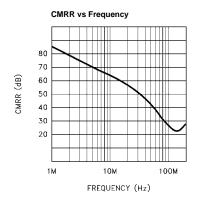

| CMRR2                  | Input Common Mode Rejection Ratio (V <sub>IN</sub> = ±2V)                   | 60   | 70   |      | dB     |

| CMRR1                  | Input Common Mode Rejection Ratio (full V <sub>IN</sub> range)              | 50   | 60   |      | dB     |

# **AC Electrical Specifications** $V_{CC} = +5V$ , $V_{EE} = -5V$ , $T_A = 25C$ , $V_{IN} = 0V$ , $R_{LOAD} = 100$ , unless otherwise specified

| PARAMETER                 | DESCRIPTION                     | MIN | TYP | MAX | UNITS  |

|---------------------------|---------------------------------|-----|-----|-----|--------|

| BW(-3dB)                  | -3dB Bandwidth (Gain =1)        |     | 150 |     | MHz    |

| SR                        | Slewrate                        |     | 400 |     | V/µs   |

| T <sub>STL</sub>          | Settling time to 1%             |     | 15  |     | ns     |

| GBWP                      | Gain bandwidth product          |     | 200 |     | MHz    |

| V <sub>REF</sub> BW(-3dB) | V <sub>REF</sub> -3dB Bandwidth |     | 130 |     | MHz    |

| V <sub>REF</sub> SR       | V <sub>REF</sub> Slewrate       |     | 100 |     | V/µsec |

| dG                        | Differential gain at 3.58MHz    |     | 0.2 |     | %      |

| dθ                        | Differential phase at 3.58MHz   |     | 0.2 |     | 0      |

# Pin Descriptions

| PIN NUMBER | PIN NAME         | FUNCTION                                                                             |

|------------|------------------|--------------------------------------------------------------------------------------|

| 1          | V <sub>FB</sub>  | Feedback input                                                                       |

| 2          | V <sub>IN</sub>  | Non-inverting input                                                                  |

| 3          | V <sub>INB</sub> | Inverting input                                                                      |

| 4          | V <sub>REF</sub> | Sets output voltage level to V <sub>REF</sub> when V <sub>IN</sub> =V <sub>INB</sub> |

| 5          | NC               |                                                                                      |

| 6          | V <sub>CC</sub>  | Positive supply voltage                                                              |

| 7          | V <sub>EE</sub>  | Negative supply voltage                                                              |

| 8          | V <sub>OUT</sub> | Output voltage                                                                       |

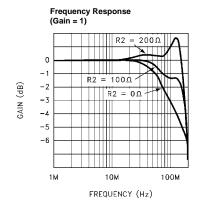

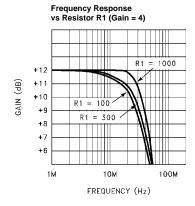

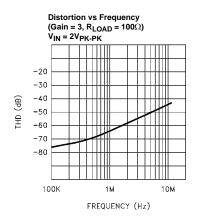

# Typical Performance Curves

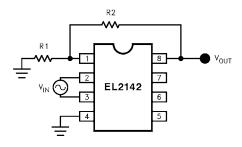

## Applications Information

#### Gain Equation

$V_{OUT} = ((R2+R1)/R1) \times (V_{IN}-V_{INB}+V_{REF})$  when R1 tied to GND

$V_{OUT} = ((R2+R1)/R1) \times (V_{IN}-V_{INB})$  when R1 tied to  $V_{REF}$

#### Choice of Feedback Resistor

For a gain of one,  $V_{OUT}$  may be shorted back to  $V_{FB}$ , but  $100\Omega$ - $200\Omega$  improves the bandwidth. For gains greater than

one, there is little to be gained from choosing resistor R1 value below  $200\Omega$ , for it would only result in increased power dissipation and potential signal distortion. Above  $200\Omega$ , the bandwidth response will develop some peaking (for a gain of one), but substantially higher R1 values may be used for higher voltage gains, such as up to  $1k\Omega$  at a gain of four before peaking will develop.

### **Capacitance Considerations**

As with many high bandwidth amplifiers, the EL2142 prefers not to drive highly capacitive loads. It is best if the capacitance on  $V_{OUT}$  is kept below 10pF if the user does not want gain peaking to develop. The  $V_{FB}$  node forms a potential pole in the feedback loop, so capacitance should be minimized on this node for maximum bandwidth.

The amount of capacitance tolerated on any of these nodes in an actual application will also be dependent on the gain setting and the resistor values in the feedback network.

## Typical Applications Circuits

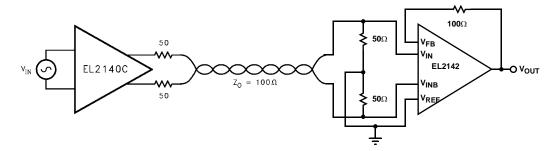

FIGURE 1. TYPICAL TWISTED PAIR APPLICATION

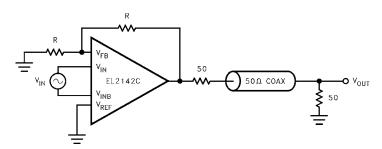

FIGURE 2. COAXIAL CABLE DRIVER PAIR APPLICATION

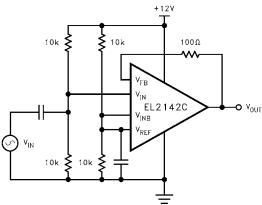

FIGURE 3. SINGLE SUPPLY RECEIVER

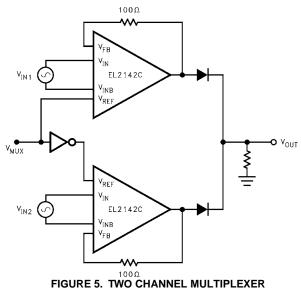

FIGURE 4. COMPENSATED LINE RECEIVER

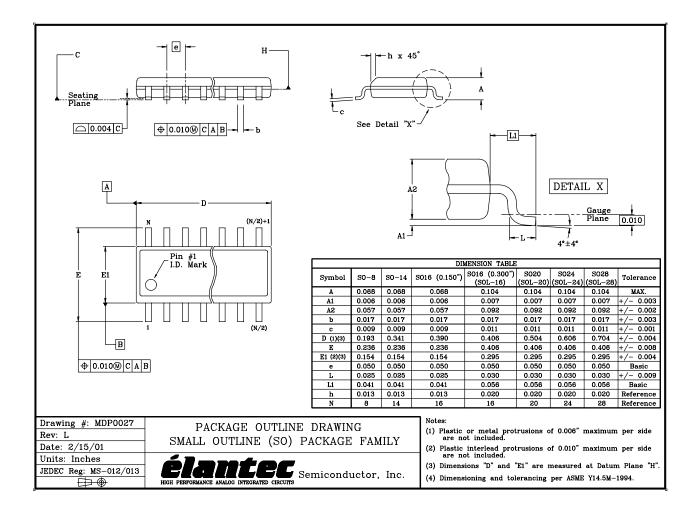

## SOIC Package Outline Drawing

NOTE: The package drawing shown here may not be the latest version. To check the latest revision, please refer to the Intersil website at <a href="http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/design/packages/index.asp>">http://www.intersil.com/des

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com