## 24 V to 220 V Precision Operational Amplifier

Data Sheet ADHV4702-1

#### **FEATURES**

Wide range of operating voltages Dual-supply: ±12 V to ±110 V

Asymmetrical supply operation: 24 V to 220 V Wide input common-mode voltage range: 3 V from rails High common-mode rejection ratio: 160 dB typical

High Ao∟: 170 dB typical

High slew rate

74 V/µs typical

24 V/µs typical with external input clamping diodes

Low input bias current: 2 pA maximum Low input offset voltage: 1 mV maximum

Low input offset voltage drift: 2  $\mu$ V/°C maximum Low input voltage noise: 8 nV/ $\sqrt{Hz}$  typical at 10 kHz

Wide small signal bandwidth: 10 MHz typical

Resistor adjustable quiescent current: 0.6 mA to 3 mA ( $V_s =$

±110 V)

Unity-gain stable Thermal monitoring

Small footprint: 12-lead, 7 mm  $\times$  7 mm LFCSP compliant with

IEC 61010-1 spacing Shutdown mode

#### **APPLICATIONS**

High-side current sensing

Automated test equipment

High voltage drivers

Piezotransducers

Digital-to-analog converter (DAC) output buffers

Light detecting and ranging (LiDAR), avalanche photodiode

(APD), single photon avalanche diode (SPAD) biasing

#### **GENERAL DESCRIPTION**

The ADHV4702-1 is a high voltage (220 V), unity-gain stable precision operational amplifier. The ADHV4702-1 offers high input impedance with low input bias current, low input offset voltage, low drift, and low noise for precision demanding applications. The next generation of proprietary semiconductor processes and innovative architecture from Analog Devices, Inc., enable this precision operational amplifier to operate from symmetrical dual supplies of  $\pm 110$  V, asymmetrical dual supplies, or a single supply of 220 V. The ADHV4702-1 requires a minimum supply voltage of  $\pm 12$  V from the reference voltage for normal operation.

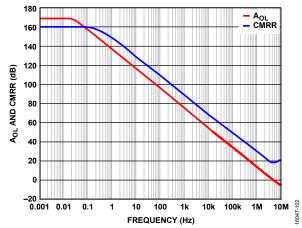

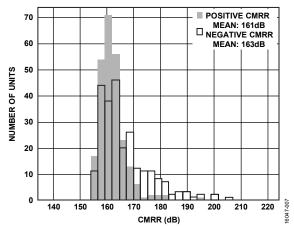

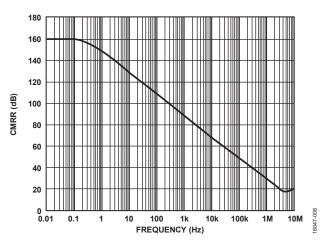

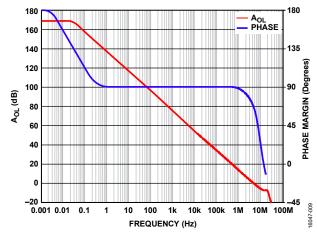

For precision performance, the ADHV4702-1 has a 170 dB typical open-loop gain ( $A_{OL}$ ) and a 160 dB typical common-mode rejection ratio (CMRR), as shown in Figure 2.

Rev. B

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

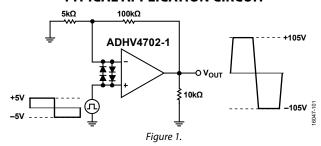

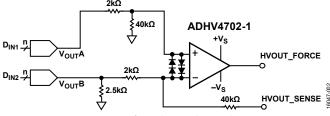

#### TYPICAL APPLICATION CIRCUIT

The ADHV4702-1 also has a 2  $\mu$ V/°C maximum input offset voltage (Vos) drift and an 8 nV/ $\sqrt{Hz}$  input voltage noise.

The exceptional dc precision of the ADHV4702-1 is complemented by excellent dynamic performance with a small signal bandwidth of 10 MHz and a slew rate of 74 V/ $\mu$ s. The ADHV4702-1 has an output current of 20 mA typical.

The ADHV4702-1 offers high voltage input common-mode swing as well as high voltage output swing, enabling precision high voltage use cases such as high-side current sensing. The ADHV4702-1 is also ideally suited for forcing a voltage in precision bias and control applications.

The ADHV4702-1 is available in a 12-lead, 7 mm  $\times$  7 mm lead frame chip scale package (LFCSP) with an exposed pad (EPAD) compliant to international electrotechnical commission (IEC) 61010-1 creepage and clearance standards. The copper EPAD provides a low thermal resistance path to improve heat dissipation and features high voltage isolation, allowing it to be safely connected to a 0 V ground plane regardless of VCC or VEE voltages. The ADHV4702-1 operates over the  $-40^{\circ}$ C to  $+85^{\circ}$ C industrial temperature range.

Figure 2. ADHV4702-1 Precision Performance

## **TABLE OF CONTENTS**

| Features                                                    |

|-------------------------------------------------------------|

| Applications                                                |

| General Description                                         |

| Typical Application Circuit                                 |

| Revision History                                            |

| Functional Block Diagram                                    |

| Specifications                                              |

| ±12 V to ±110 V Supply 4                                    |

| Absolute Maximum Ratings 6                                  |

| Maximum Power Dissipation6                                  |

| Thermal Resistance6                                         |

| ESD Caution6                                                |

| Pin Configuration and Function Descriptions                 |

| Typical Performance Characteristics                         |

| Theory of Operation                                         |

| Internal Electrostatic Discharge (ESD) Protection15         |

| Slew Boost Circuit and Protection                           |

| Digital Ground (DGND)16                                     |

| Resistor Adjustable Quiescent Current (RADJ)16              |

| REVISION HISTORY                                            |

| 1/2020—Rev. A to Rev. B                                     |

| Changes to General Description Section 1                    |

| Change to CMRR Parameter in Table 1                         |

| Added Figure 33 and Figure 34; Renumbered Sequentially      |

| Change to External Compensation and Capacitive Load (CLOAD) |

| Driving Section                                             |

| Changes to Power Supply and Decoupling Section              |

| 3/2019—Rev. 0 to Rev. A                                     |

| Changes to Figure 59                                        |

| Changes to Ordering Guide                                   |

|                                                             |

11/2018—Revision 0: Initial Version

| Shutdown Pin (SD) 1                                       | 1  |

|-----------------------------------------------------------|----|

| Temperature Monitor (TMP) 1                               | 7  |

| Overtemperature Protection 1                              | 7  |

| Output Current Drive and Short-Circuit Protection 1       | 8  |

| External Compensation and Capacitive Load (CLOAD) Driving | _  |

| Safe Operating Area1                                      | 9  |

| LFCSP Package and High Voltage Pin Spacing1               | 9  |

| Exposed Pad (EPAD)1                                       | 9  |

| Applications Information                                  | 0  |

| Power Supply and Decoupling2                              | 0  |

| High Voltage Guard Ring2                                  | C  |

| High Voltage DAC Voltage Subtractor2                      | C  |

| High Current Output Driver2                               | C  |

| Signal Range Extender2                                    | 0  |

| Outline Dimensions                                        | .1 |

| Ordaring Cuida                                            | 1  |

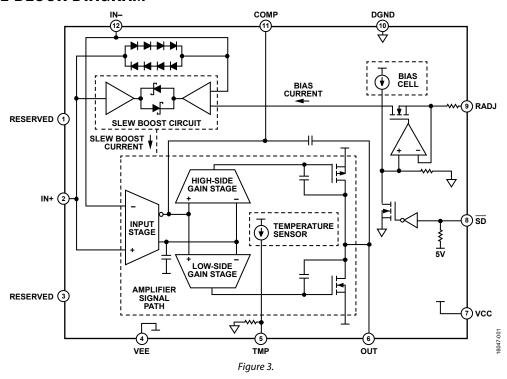

## **FUNCTIONAL BLOCK DIAGRAM**

### **SPECIFICATIONS**

### ±12 V TO ±110 V SUPPLY

Supply voltage  $(V_S) = \pm 12 \text{ V}$  to  $\pm 110 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$  with an EPAD connected to a 0 V analog ground (AGND), DGND pin tied to 0 V AGND,  $R_{ADJ}{}^{1} = 0 \Omega$ , gain  $(A_V) = 1$ , feedback resistor  $(R_F) = 100 \text{ k}\Omega$ , and load resistance  $(R_{LOAD}) = 10 \text{ k}\Omega$ , unless otherwise noted.

Table 1.

| Parameter                       | Test Conditions/Comments                                                   | Min  | Тур   | Max  | Unit   |

|---------------------------------|----------------------------------------------------------------------------|------|-------|------|--------|

| DYNAMIC PERFORMANCE             |                                                                            |      |       |      |        |

| –3 dB Bandwidth                 | $A_V = 1$ , output voltage ( $V_{OUT}$ ) = 200 mV p-p, $R_F = 0 \Omega$    |      | 10    |      | MHz    |

| Slew Rate                       | $A_V = 20$ , $V_{OUT} = 200 \text{ V p-p}$ , 20% to 80%                    |      | 74    |      | V/µs   |

|                                 | $A_V = 20$ , $V_{OUT} = 200 \text{ V p-p}$ , 20% to 80%, with external     |      | 24    |      | V/µs   |

|                                 | input clamping diodes <sup>2</sup>                                         |      |       |      |        |

| Settling Time to 0.1%           | $A_V = 1$ , $V_{OUT} = 40 \text{ V p-p}$ , $R_F = 0 \Omega$                |      | 8.4   |      | μs     |

|                                 | $A_V = 20, V_{OUT} = 40 \text{ V p-p}$                                     |      | 6.2   |      | μs     |

|                                 | $A_V = 40, V_{OUT} = 40 \text{ V p-p}$                                     |      | 13    |      | μs     |

| NOISE PERFORMANCE               |                                                                            |      |       |      |        |

| Input Voltage Noise             | Frequency = 10 kHz                                                         |      | 8     |      | nV/√Hz |

| Input Voltage Noise 1/f Corner  |                                                                            |      | 10    |      | Hz     |

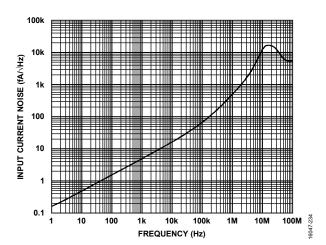

| Input Current Noise             | Frequency = 40 Hz                                                          |      | 1     |      | fA/√Hz |

| DC PERFORMANCE                  |                                                                            |      |       |      |        |

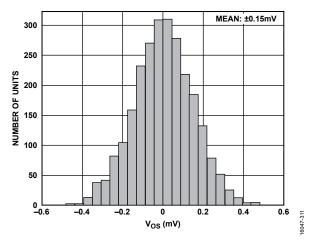

| Input Offset Voltage            |                                                                            | -1   | ±0.15 | +1   | mV     |

| Drift                           | $V_S = \pm 110 \text{ V}, T_A = 25^{\circ}\text{C to } 85^{\circ}\text{C}$ | -2   | ±0.25 | +2   | μV/°C  |

|                                 | $V_S = \pm 12 \text{ V}, T_A = 25^{\circ}\text{C to } 85^{\circ}\text{C}$  | -3   | ±0.25 | +3   | μV/°C  |

| Input Bias Current              | T <sub>A</sub> = 25°C                                                      | -2   | ±0.3  | +2   | рА     |

|                                 | T <sub>A</sub> = 85°C                                                      | -100 | ±19   | +100 | рА     |

| Drift                           | $T_A = 25$ °C to 85°C                                                      |      | ±0.3  |      | pA/°C  |

| Input Offset Current            | T <sub>A</sub> = 25°C                                                      | -2   | ±0.15 | +2   | рА     |

|                                 | T <sub>A</sub> = 85°C                                                      | -50  | ±8    | +50  | рА     |

| Drift                           | $T_A = 25$ °C to 85°C                                                      |      | ±0.13 |      | pA/°C  |

| Open-Loop Gain                  | $V_S = \pm 110 \text{ V}$                                                  | 146  | 170   |      | dB     |

|                                 | $V_S = \pm 12 \text{ V}$                                                   | 130  | 150   |      | dB     |

| INPUT CHARACTERISTICS           |                                                                            |      |       |      |        |

| Input Resistance                |                                                                            |      |       |      |        |

| Common-Mode                     | Common-mode voltage $(V_{CM}) = -60 \text{ V}$ to $+60 \text{ V}$          |      | 45    |      | ΤΩ     |

|                                 | $V_{CM} = -90 \text{ V to } +90 \text{ V}$                                 |      | 30    |      | ΤΩ     |

| Differential                    |                                                                            |      | 4.2   |      | ΤΩ     |

| Input Capacitance               |                                                                            |      |       |      |        |

| Common-Mode                     |                                                                            |      | 7.9   |      | pF     |

| Differential                    |                                                                            |      | 17.9  |      | pF     |

| Input Common-Mode Voltage Range |                                                                            |      | ±107  |      | ٧      |

| CMRR                            | $V_{CM} = -70 \text{ V to } +70 \text{ V}$                                 | 140  | 160   |      | dB     |

| SHUTDOWN PIN (SD)               |                                                                            |      |       |      |        |

| SD Input Voltage                |                                                                            |      |       |      |        |

| Low                             | Disabled                                                                   |      |       | 0.8  | V      |

| High                            | Enabled                                                                    | 1.6  |       |      | V      |

| SD Input Current                |                                                                            |      |       |      |        |

| Low                             | $\overline{SD} = 0 \text{ V}$                                              |      | -11   |      | μΑ     |

| High                            | $\overline{SD} = 5 \text{ V}$                                              |      | -1    |      | μΑ     |

| 1 11911                         | J.J. J. V                                                                  |      | •     |      | μ, ι   |

| Parameter                                    | Test Conditions/Comments                                                                                      | Min | Тур    | Max  | Unit  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----|--------|------|-------|

| OUTPUT CHARACTERISTICS                       |                                                                                                               |     |        |      |       |

| Output Voltage Range                         | $R_{LOAD} = 5 \text{ k}\Omega$ , $T_A = -40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$                         |     |        |      |       |

| High                                         |                                                                                                               | 108 | 108.5  |      | V     |

| Low                                          |                                                                                                               |     | -108.5 | -108 | V     |

| Output Current                               |                                                                                                               |     | 20     |      | mA    |

| THERMAL MONITOR                              |                                                                                                               |     |        |      |       |

| TMP Pin Voltage <sup>3</sup>                 | T <sub>A</sub> = 25°C                                                                                         |     | 1.9    |      | V     |

| TMP Pin Voltage Drift                        | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                           |     | -4.5   |      | mV/°C |

| POWER SUPPLY                                 |                                                                                                               |     |        |      |       |

| Operating Range                              | Symmetrical and asymmetrical supplies                                                                         | 24  |        | 220  | V     |

| Quiescent Current                            |                                                                                                               |     |        |      |       |

| $\overline{SD} = 5 \text{ V (Enabled)}^4$    | $R_{ADJ}^{1} = 0 \Omega$ , $T_{A} = 25^{\circ}C$ , $V_{S} = \pm 110 V$                                        |     | 3      | 3.3  | mA    |

|                                              | $R_{ADJ}^{1} = 0 \Omega$ , $T_{A} = 25^{\circ}C$ , $V_{S} = \pm 12 V$                                         |     | 2.7    | 3.3  | mA    |

|                                              | $R_{ADJ}^{1} = 0 \Omega$ , $T_{A} = -40^{\circ}C$ to $+85^{\circ}C$                                           |     |        | 3.3  | mA    |

|                                              | $R_{ADJ}^{1} = 50 \text{ k}\Omega$ , $T_{A} = 25^{\circ}\text{C}$ , $V_{S} = \pm 110 \text{ V}$               |     | 0.9    | 1    | mA    |

|                                              | $R_{ADJ}^{1} = 50 \text{ k}\Omega$ , $T_{A} = 25^{\circ}\text{C}$ , $V_{S} = \pm 12 \text{ V}$                |     | 0.8    | 1    | mA    |

|                                              | $R_{ADJ}^{1} = 50 \text{ k}\Omega$ , $T_{A} = -40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$                   |     |        | 1    | mA    |

|                                              | $R_{ADJ}^{1} = 100 \text{ k}\Omega$ , $T_{A} = 25^{\circ}\text{C}$ , $V_{S} = \pm 110 \text{ V}$              |     | 0.6    |      | mA    |

| $\overline{SD} = 0 \text{ V (Disabled)}$     |                                                                                                               |     | 0.18   | 0.2  | mA    |

| Positive Power Supply Rejection Ratio (PSRR) | Positive supply voltage $(+V_s) = 107 \text{ V}$ to 112.5 V, negative supply voltage $(-V_s) = 110 \text{ V}$ | 130 | 155    |      | dB    |

|                                              | $+V_S = 10 \text{ V to } 14 \text{ V}, -V_S = -12 \text{ V}$                                                  | 110 | 130    |      | dB    |

| Negative Power Supply Rejection Ratio        | $+V_S = 110 \text{ V}, -V_S = -107 \text{ V to } -112.5 \text{ V}$                                            | 130 | 155    |      | dB    |

|                                              | $+V_S = 12 \text{ V}, -V_S = -10 \text{ V to } -14 \text{ V}$                                                 | 110 | 130    |      | dB    |

<sup>&</sup>lt;sup>1</sup> R<sub>ADJ</sub> is a resistor that connects the RADJ pin to DGND.

<sup>2</sup> This slew rate result is tested while the ADHV4702-1 inputs are clamped at the forward-biased voltage of two diodes using ON Semiconductor\* SBAV199LT1G. For more information, see the Slew Boost Circuit and Protection section.

<sup>&</sup>lt;sup>3</sup> The TMP pin voltage may have device to device variation. For more information, see the Temperature Monitor (TMP) section.

<sup>4</sup> This specification is for quiescent current only. For supply current or dynamic supply current information, see the Theory of Operation section.

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                                        | Rating               |

|--------------------------------------------------|----------------------|

| Supply Voltage (VCC to VEE)                      | 225 V                |

| Output Voltage                                   | VCC to VEE           |

| Common-Mode Input Voltage                        | VCC to VEE           |

| Differential Input Voltage                       | ±2.0 V               |

| Input Current                                    | ±5 mA                |

| DGND Voltage                                     | VCC – 12 V to VEE    |

| Voltage                                          |                      |

| RESERVED, SD, and TMP Pins                       | DGND to DGND + 6 V   |

| COMP Pin                                         | VCC – 5 V to VCC     |

| RADJ Pin                                         | DGND to DGND + 0.6 V |

| Storage Temperature Range                        | −65°C to +150°C      |

| Operating Temperature Range                      | −40°C to +85°C       |

| Lead Temperature (Soldering 10 sec) <sup>1</sup> | 260°C                |

| Junction Temperature (T <sub>J</sub> )           | 150°C                |

<sup>&</sup>lt;sup>1</sup> See IPC/JEDEC J-STD-020 for more information.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **MAXIMUM POWER DISSIPATION**

The maximum safe power dissipation in the package is limited by the associated rise in  $T_{\rm I}$  on the die. At approximately 150°C, which is the glass transition temperature, the plastic begins to change its properties. Exceeding a  $T_{\rm I}$  of 150°C can result in changes in the silicon devices, potentially causing failure. Table 3 shows the junction-to-case thermal resistance ( $\theta_{\rm JC}$ ) for the LFCSP. For more detailed information on power dissipation and thermal management, see the Applications Information section.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection, junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

**Table 3. Thermal Resistance**

| Package Type         | θ <sub>JA</sub> | θις | Unit |

|----------------------|-----------------|-----|------|

| CP-12-8 <sup>1</sup> | 37              | 1   | °C/W |

$<sup>^1</sup>$  The data is collected from a 2S2P board. A cold plate is attached to the bottom side of the PCB using 100  $\mu$ m thermal interface material (TIM) for  $\theta_{JC}$  simulation. See JEDEC standard for additional information.

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

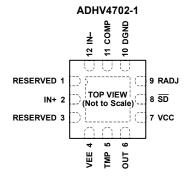

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

- NOTES

1. RESERVED. THESE PINS ARE INTERNALLY CONNECTED. FLOAT OR TIE THESE PINS TO THE DIGITAL GROUND.

2. EXPOSED THERMAL PAD. NO INTERNAL ELECTRICAL CONNECTION. TIE EPAD TO EXTERNAL GROUND PLANE AND/OR HEAT SINK FOR THERMAL MANAGEMENT.

Figure 4. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                        |

|---------|----------|------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3    | RESERVED | Reserved. These pins are internally connected. Float or connect these pins to the digital ground.                                  |

| 2       | IN+      | Noninverting Input.                                                                                                                |

| 4       | VEE      | Negative Power Supply Input.                                                                                                       |

| 5       | TMP      | Temperature Monitor Output.                                                                                                        |

| 6       | OUT      | Output.                                                                                                                            |

| 7       | VCC      | Positive Power Supply Input.                                                                                                       |

| 8       | SD       | Shutdown (Active Low). SD is referenced to DGND.                                                                                   |

| 9       | RADJ     | Resistor Adjustable Quiescent Current. Connect RADJ to DGND to fully bias the amplifier.                                           |

| 10      | DGND     | Logic Reference for RADJ and SD. Connect DGND to 0 V analog ground.                                                                |

| 11      | COMP     | External Compensation.                                                                                                             |

| 12      | IN-      | Inverting Input.                                                                                                                   |

|         | EPAD     | Exposed Thermal Pad. No internal electrical connection. Tie EPAD to external ground plane and/or heat sink for thermal management. |

### TYPICAL PERFORMANCE CHARACTERISTICS

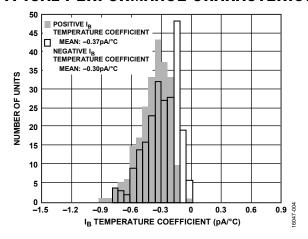

Figure 5. Positive and Negative Input Bias (I<sub>B</sub>) Current Drift Distribution,  $T_A=25\,^{\circ}\text{C}$ ,  $V_S=\pm110\,\text{V}$ ,  $V_{CM}=0\,\text{V}$ ,  $\Delta T_A=60\,^{\circ}\text{C}$ ,  $R_{ADJ}=0\,\Omega$

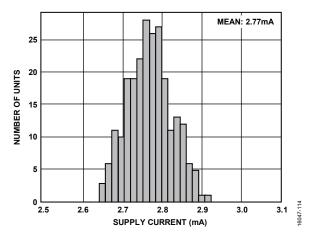

Figure 6. Supply Current Distribution,  $T_A = 25$ °C,  $V_S = \pm 110$  V,  $R_{ADJ} = 0$   $\Omega$

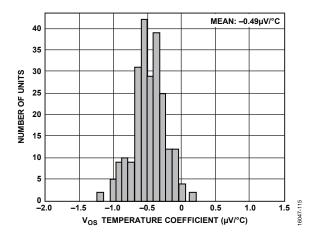

Figure 7. Input Offset Voltage Drift Distribution,  $T_A = 25$  °C,  $V_S = \pm 110$  V,  $V_{CM} = 0$  V,  $\Delta T_J = 60$  °C,  $R_{ADJ} = 0$   $\Omega$

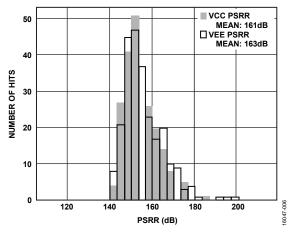

Figure 8. PSRR Distribution,  $T_A = 25$ °C,  $V_S = \pm 110$  V,  $R_{ADJ} = 0$   $\Omega$

Figure 9. CMRR Distribution,  $T_A = 25$ °C,  $V_S = \pm 110$  V,  $R_{ADJ} = 0$   $\Omega$

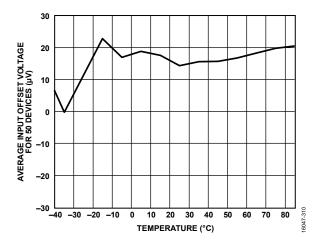

Figure 10. Average Input Offset Voltage for 50 Devices vs. Temperature,  $V_S = \pm 110 \text{ V}$

Figure 11. Input Offset Voltage Distribution,  $T_A=25$  °C,  $V_S=\pm110$  V,  $V_{CM}=0$  V,  $R_{ADJ}=0$   $\Omega$

Figure 12. CMRR vs. Frequency,  $T_A = 25^{\circ}\text{C}$ ,  $V_S = \pm 110 \text{ V}$ ,  $R_{\text{LOAD}} = 10 \text{ k}\Omega$ ,  $R_{\text{ADJ}} = 0 \Omega$

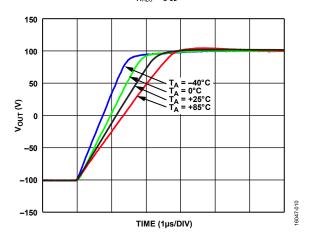

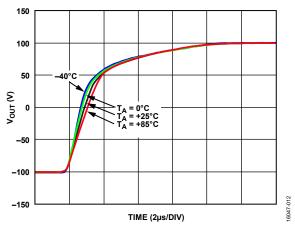

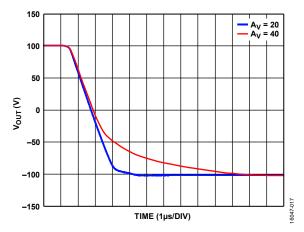

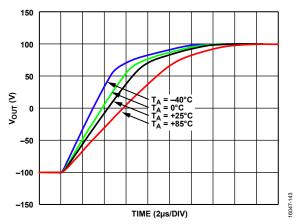

Figure 13. Large Signal Pulse Response at Various  $T_{A_r}$  Rising Edge,  $A_V=20$ ,  $V_S=\pm 110~V, V_{OUT}=200~V~p-p, R_F=100~k\Omega, R_{LOAD}=10~k\Omega, R_{ADJ}=0~\Omega$

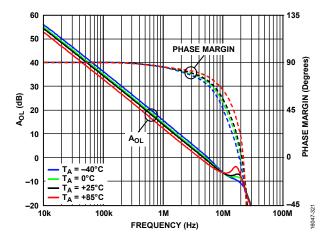

Figure 14. A<sub>OL</sub> and Phase Margin vs. Frequency at Various T<sub>A</sub>, V<sub>S</sub> =  $\pm 110$  V,  $R_{ADJ} = 0$   $\Omega$

Figure 15.  $A_{OL}$  and Phase Margin vs. Frequency,  $T_A=25\,^{\circ}\text{C}$ ,  $V_S=\pm110\,\text{V}$ ,  $R_{ADJ}=0\,\Omega$

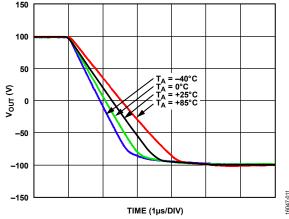

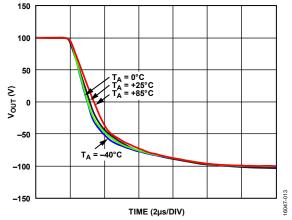

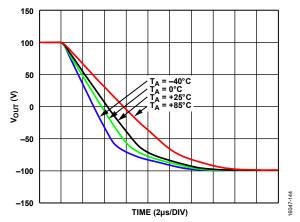

Figure 16. Large Signal Pulse Response at Various  $T_{A_F}$  Falling Edge,  $A_V = 20$ ,  $V_S = \pm 110 \text{ V}$ ,  $V_{OUT} = 200 \text{ V}$  p-p,  $R_F = 100 \text{ k}\Omega$ ,  $R_{LOAD} = 10 \text{ k}\Omega$ ,  $R_{ADJ} = 0 \Omega$

Figure 17. Large Signal Pulse Response at Various  $T_{A_I}$  Rising Edge,  $A_V$  = 40,  $V_S$  =  $\pm 110$  V,  $V_{OUT}$  = 200 V p-p,  $R_F$  = 100 k $\Omega$ ,  $R_{LOAD}$  = 10 k $\Omega$ ,  $R_{ADJ}$  = 0  $\Omega$

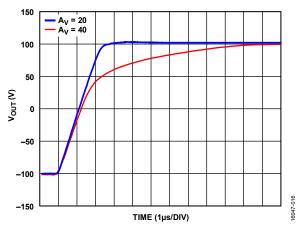

Figure 18. Large Signal Pulse Response at Various Gains, Rising Edge,  $T_A=25\,^{\circ}\text{C}$ ,  $V_S=\pm110\,\text{V}$ ,  $V_{OUT}=200\,\text{V}$  p-p,  $R_F=100\,\text{k}\Omega$ ,  $R_{LOAD}=10\,\text{k}\Omega$ ,  $R_{ADJ}=0\,\Omega$

Figure 19. Large Signal Pulse Response at Various Gains,  $T_A = 25^{\circ}\text{C}$ ,  $V_S = \pm 110 \text{ V}$ ,  $V_{\text{OUT}} = 200 \text{ V}$  p-p,  $R_F = 100 \text{ k}\Omega$ ,  $R_{\text{LOAD}} = 10 \text{ k}\Omega$ ,  $R_{\text{ADJ}} = 0 \Omega$

Figure 20. Large Signal Pulse Response at Various  $T_A$ , Falling Edge,  $A_V$  = 40,  $V_S$  =  $\pm 110$  V,  $V_{OUT}$  = 200 V p-p,  $R_F$  = 100 k $\Omega$ ,  $R_{LOAD}$  = 10 k $\Omega$ ,  $R_{ADJ}$  = 0  $\Omega$

Figure 21. Large Signal Pulse Response at Various Gains, Falling Edge,  $T_A=25$ °C,  $V_S=\pm110$  V,  $V_{OUT}=200$  V p-p,  $R_F=100$  k $\Omega$ ,  $R_{LOAD}=10$  k $\Omega$ ,  $R_{ADJ}=0$   $\Omega$

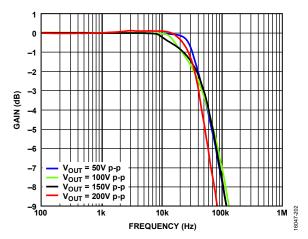

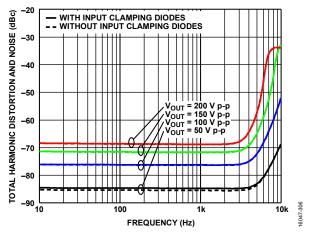

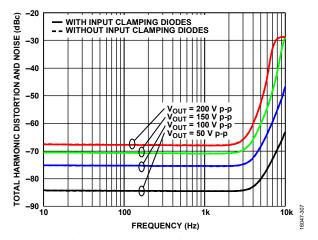

Figure 22. Large Signal Frequency Response at Various Output Swings with Input Clamping Diodes (See the Slew Boost Circuit and Protection Section),  $T_A=25^{\circ}\text{C}, A_V=40, V_S=\pm 110 \text{ V}, R_F=100 \text{ k}\Omega, R_{LOAD}=10 \text{ k}\Omega, R_{RDJ}=0 \Omega$

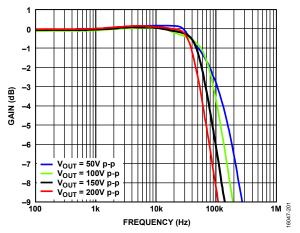

Figure 23. Large Signal Frequency Response at Various Output Swings with Input Clamping Diodes (See the Slew Boost Circuit and Protection Section),  $T_A = 25\,^{\circ}\text{C}$ ,  $A_V = 20$ ,  $V_S = \pm 110\,\text{V}$ ,  $R_F = 100\,\text{k}\Omega$ ,  $R_{LOAD} = 10\,\text{k}\Omega$ ,  $R_{RDJ} = 0\,\Omega$

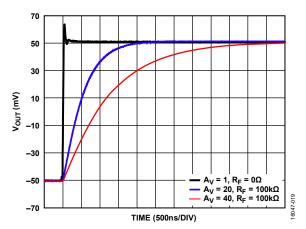

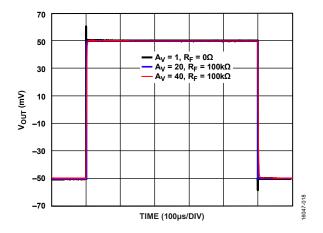

Figure 24. Small Signal Pulse Response at Various Gains, Rising Edge,  $T_A = 25$  °C,  $V_S = \pm 110$  V,  $V_{OUT} = 100$  mV p-p,  $R_{LOAD} = 10$  k $\Omega$ ,  $R_{ADJ} = 0$   $\Omega$

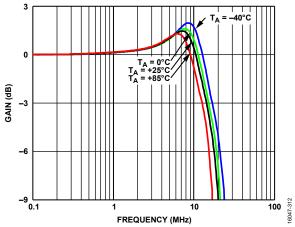

Figure 25. Small Signal Frequency Response at Various  $T_A$ ,  $A_V=1$ ,  $V_S=\pm 110$  V,  $V_{OUT}=100$  mV p-p,  $R_L=10$  k $\Omega$ ,  $R_{ADJ}=0$   $\Omega$

Figure 26. Small Signal Pulse Response at Various Gains,  $T_A = 25$ °C,  $V_S = 110$  V,  $V_{OUT} = 100$  mV p-p,  $R_{LOAD} = 10$  k $\Omega$ ,  $R_{ADJ} = 0$   $\Omega$

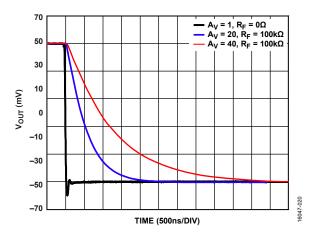

Figure 27. Small Signal Pulse Response at Various Gains, Falling Edge,  $T_A = 25$ °C,  $V_S = \pm 110$  V,  $V_{OUT} = 100$  mV p-p,  $R_{LOAD} = 10$  k $\Omega$ ,  $R_{ADJ} = 0$   $\Omega$

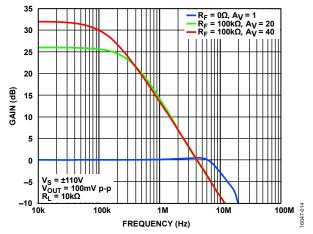

Figure 28. Small Signal Frequency Response at Various Gains,  $T_A$  = 25°C,  $V_S$  = ±110 V,  $V_{OUT}$  = 100 mV p-p,  $R_L$  = 10 k $\Omega$ ,  $R_{ADJ}$  = 0  $\Omega$

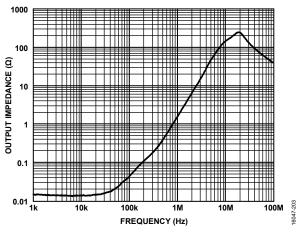

Figure 29. Output Impedance vs. Frequency,  $T_A = 25$ °C,  $A_V = 1$ ,  $V_S = \pm 110$  V,  $V_{OUT} = 100$  mV p-p,  $R_F = 0$   $\Omega$ ,  $R_{ADJ} = 0$   $\Omega$

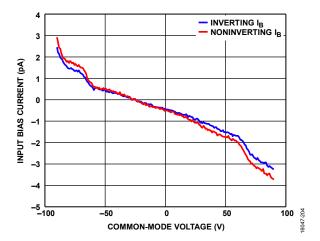

Figure 30. Input Bias Current vs. Common-Mode Voltage,  $T_A=25$  °C,  $V_S=\pm110$  V,  $R_{ADJ}=0$   $\Omega$

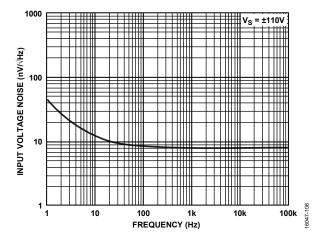

Figure 31. Input Voltage Noise vs. Frequency,  $T_A = 25$  °C,  $V_S = \pm 110$ ,  $R_{ADJ} = 0 \Omega$

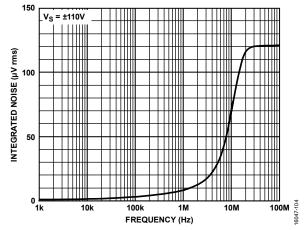

Figure 32. Integrated Noise vs. Frequency,  $T_A = 25$  °C,  $V_S = \pm 110$  V,  $R_{ADJ} = 0$   $\Omega$

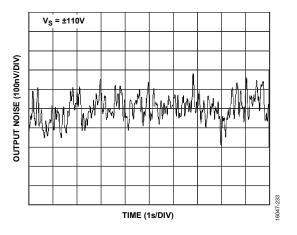

Figure 33. 0.1 Hz to 10 Hz Noise

Figure 34. Input Current Noise vs. Frequency

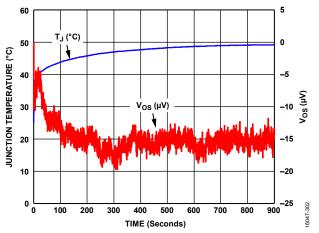

Figure 35. Offset Voltage Warmup Drift and  $T_J$ ,  $V_S = \pm 110$ ,  $R_{ADJ} = 0 \Omega$

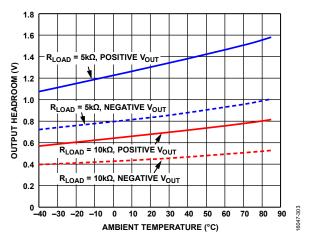

Figure 36. Output Headroom vs. Ambient Temperature at Various  $R_{LOAD}$ ,  $V_S = \pm 110 \text{ V}$ ,  $R_{ADJ} = 0 \Omega$

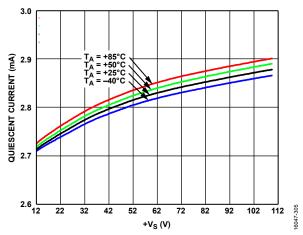

Figure 37. Quiescent Current vs. Positive Supply Voltage at Various  $T_{A_{\nu}}$   $R_{ADJ} = 0~\Omega$

Figure 38. Total Harmonic Distortion and Noise vs. Frequency at Various Large Output Swings,  $T_A=25^{\circ}\text{C}$ ,  $A_V=20$ ,  $V_S=\pm110$  V,  $R_F=100$  k $\Omega$ ,  $R_{LOAD}=10$  k $\Omega$ ,  $R_{ADJ}=0$   $\Omega$

Figure 39. Total Harmonic Distortion and Noise vs. Frequency at Various Large Output Swings,  $T_A=25^{\circ}\text{C}$ ,  $A_V=40$ ,  $V_S=\pm110$  V,  $R_F=100$  k $\Omega$ ,  $R_{LOAD}=10$  k $\Omega$ ,  $R_{ADJ}=0$   $\Omega$

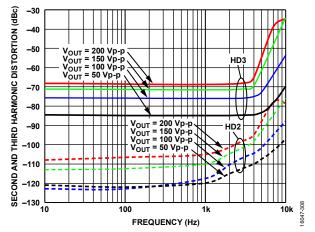

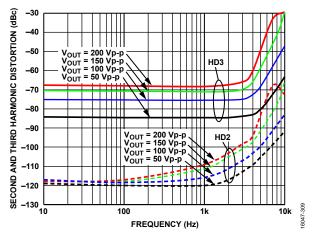

Figure 40. Second Harmonic Distortion (HD2) and Third Harmonic Distortion (HD3) vs. Frequency at Various Output Swings,  $T_A=25^{\circ}\text{C}$ ,  $A_V=20$ ,  $V_S=\pm110$  V,  $R_F=100$  k $\Omega$ ,  $R_{LOAD}=10$  k $\Omega$ ,  $R_{ADJ}=0$   $\Omega$

Figure 41. Second Harmonic Distortion (HD2) and Third Harmonic Distortion (HD3) vs. Frequency at Various Output Swings,  $T_A=25^{\circ}\text{C}$ ,  $A_V=40$ ,  $V_S=\pm110\text{ V}$ ,  $R_F=100\text{ k}\Omega$ ,  $R_{LOAD}=10\text{ k}\Omega$ ,  $R_{ADJ}=0\Omega$

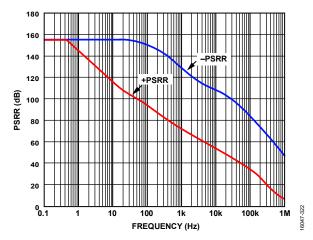

Figure 42. PSRR vs. Frequency,  $T_A=25^{\circ}\text{C},\ V_S=\pm110\ V,\ R_{LOAD}=10\ k\Omega,\ R_{ADJ}=0\ \Omega$

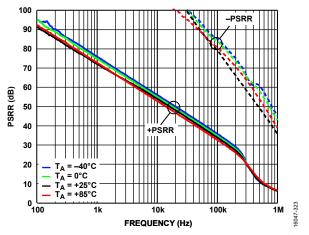

Figure 43. PSRR vs. Frequency at Various  $T_{A}$ ,  $V_{S}=\pm 110$  V,  $R_{LOAD}=10$  k $\Omega$ ,  $R_{ADJ}=0$   $\Omega$

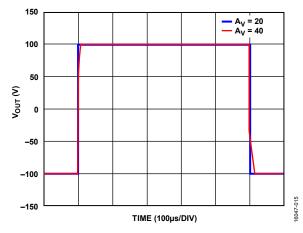

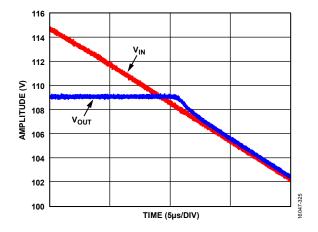

Figure 44. Output Overdrive Recovery,  $V_S$  =  $\pm 110$  V,  $A_V$  = 40,  $R_{LOAD}$  = 10 k $\Omega$ ,  $R_{ADJ}$  = 0  $\Omega$

### THEORY OF OPERATION

The ADHV4702-1 is a high voltage (220 V) precision amplifier designed using the next generation of proprietary bipolar/ complementary metal-oxide semiconductor (CMOS)/laterally diffused metal-oxide semiconductor (BCDMOS) process from Analog Devices. Figure 3 shows the functional block diagram. The input stage architecture offers the advantages of high input impedance with low input bias current, low input offset voltage, low drift, and low noise for precision demanding applications, such as automated test equipment (ATE).

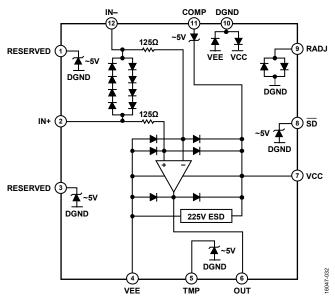

## INTERNAL ELECTROSTATIC DISCHARGE (ESD) PROTECTION

As shown in Figure 45, the ADHV4702-1 has an internal ESD configuration to prevent damage due to overvoltage. The ESD protection circuitry involves current steering diodes connected from the input and output pins to the power supply rails. The ADHV4702-1 also includes internal input clamping diodes across the inverting and noninverting inputs to prevent large differential input voltages from damaging the input stage transistors. This input clamping circuit greatly reduces the input impedance for differential input voltages greater than the forward-biased voltage ( $V_F$ ) of four diodes.

The ESD protection circuitry remains inactive under normal operation. To avoid forward biasing the ESD diodes, do not overdrive the pin voltages above the absolute maximum ratings, and ensure that the input differential voltage does not exceed 4  $V_{\rm F}$ . Additional external input clamping diodes may be required to protect the slew boost circuit. See the Slew Boost Circuit and Protection section.

Figure 45. Simplified ESD Configuration

#### **SLEW BOOST CIRCUIT AND PROTECTION**

The ADHV4702-1 uses a supplementary slew boosting circuit to achieve its typical slew rate of 74 V/ $\mu$ s across a 200 V p-p output range at unity gain. This slew boosting circuit works by sensing the differential input voltage of the amplifier and converting this voltage into a dynamic current to help drive capacitances within the signal path of the amplifier. With greater input voltage across the inputs, more dynamic current is produced, which enables the amplifier to slew faster. The current produced by the slew boosting circuit transmits to all stages of the amplifier during slewing.

Internally, the ADHV4702-1 contains differential input voltage clamps that limit transient differential signals to 4  $V_{\text{F}}$ , placing an upper limit on the slew boost. Large differential input voltages (which can be occur with signal frequencies approaching the full power bandwidth) trigger the slew boosting circuit, resulting in an increased dynamic supply current. The relationship between slew rate and full power bandwidth ( $f_{\text{M}}$ ) is given in the following equation:

$$SR = V_O \times 2\pi f_M$$

where  $V_O$  is the peak output voltage.

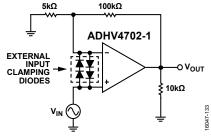

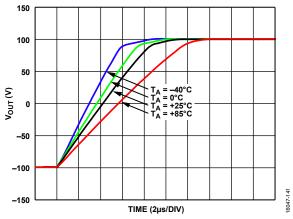

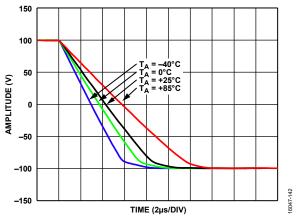

When operating continuously at or near full power bandwidth, the increased supply current may cause an increase in T<sub>J</sub> beyond the safe operating temperature, resulting in device damage. The dynamic safe operating area (SOA) for the EVAL-ADHV4702-1CPZ evaluation board is shown in Figure 61 in the Safe Operating Area section. The dynamic SOA shows the connection between the output swing and the maximum input/output frequency for pulse response. To expand the SOA curve, use additional thermal management or limit the differential voltage across the inputs to 2  $V_{\text{F}}$  with external diodes, which limits the current produced by the slew boosting circuit and reduces the internal power dissipation. Clamping the differential input voltage of the ADHV4702-1 in this way protects the amplifier in dynamic operation but limits slew rate and large signal bandwidth. Figure 46 shows a simplified schematic with external input clamping diodes, and Figure 47 to Figure 50 show the large signal pulse response at various temperatures and gains while the ADHV4702-1 inputs are clamped by two ON Semiconductor SBAV199LT1G diode pairs at 2 V<sub>F</sub>.

Figure 46. External Input Clamping Diodes Schematic

Figure 47. Large Signal Pulse Response at Various  $T_A$  with Two-Diode Forward Voltages, Rising Edge,  $A_V = 20$ ,  $V_S = \pm 110$  V,  $V_{OUT} = 200$  V p-p,  $R_F = 100$  k $\Omega$ ,  $R_{LOAD} = 10$  k $\Omega$ ,  $R_{ADJ} = 0$   $\Omega$

Figure 48. Large Signal Pulse Response at Various  $T_A$  with Two-Diode Forward Voltages, Falling Edge,  $A_V = 20$ ,  $V_S = \pm 110$  V,  $V_{OUT} = 200$  V p-p,  $R_F = 100$  k $\Omega$ ,  $R_{LOAD} = 10$  k $\Omega$ ,  $R_{ADJ} = 0$   $\Omega$

Figure 49. Large Signal Pulse Response at Various  $T_A$  with Two-Diode Forward Voltages, Rising Edge,  $A_V = 40$ ,  $V_S = \pm 110$  V,  $V_{OUT} = 200$  V p-p,  $R_F = 100$  k $\Omega$ ,  $R_{LOAD} = 10$  k $\Omega$ ,  $R_{ADJ} = 0$   $\Omega$

Figure 50. Large Signal Pulse Response at Various  $T_A$  with Two-Diode Forward Voltages, Falling Edge,  $A_V = 40$ ,  $V_S = \pm 110$  V,  $V_{OUT} = 200$  V p-p,  $R_F = 100$  k $\Omega$ ,  $R_{LOAD} = 10$  k $\Omega$ ,  $R_{ADJ} = 0$   $\Omega$

#### **DIGITAL GROUND (DGND)**

DGND is the reference for all low voltage pins of the amplifier (RADJ, TMP, and  $\overline{SD}$ ) and serves as a signal ground for communication to a microprocessor or other low voltage logic circuit. Connect DGND to a 0 V digital ground or analog ground. Do not float DGND.

## RESISTOR ADJUSTABLE QUIESCENT CURRENT (RADJ)

To reduce further power consumption, the quiescent current of the ADHV4702-1 can be adjusted by placing a resistor ( $R_{ADJ}$ ) between the RADJ pin and DGND.

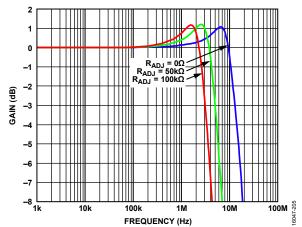

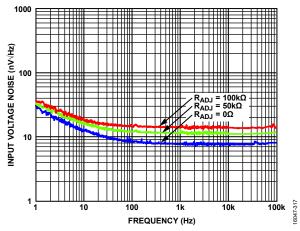

To fully bias the amplifier, short the RADJ pin directly to DGND to allow maximum dynamic performance. To bias the amplifier with minimum quiescent power consumption, place a 100 k $\Omega$  resistor from RADJ to DGND. This resistor reduces quiescent supply current to approximately 0.6 mA. Operating the amplifier at a lower quiescent current has minimal effect on dc performance but can result in an associated reduction in dynamic performance, such as bandwidth and noise. Figure 51 and Figure 52 show the small signal frequency response and noise performance at various  $R_{\text{ADJ}}$  values.

Figure 51. Small Signal Frequency Response at Various R<sub>ADJ</sub>,  $T_A$  = 25°C,  $A_V$  = 1,  $V_S$  =  $\pm 110$  V,  $V_{OUT}$  = 100 mV p-p,  $R_F$  = 0  $\Omega$ ,  $R_{LOAD}$  = 10 k $\Omega$

Figure 52. Input Voltage Noise at Various  $R_{ADJ}$ ,  $T_A = 25$ °C,  $V_S = \pm 110$

#### SHUTDOWN PIN (SD)

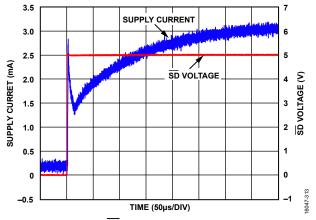

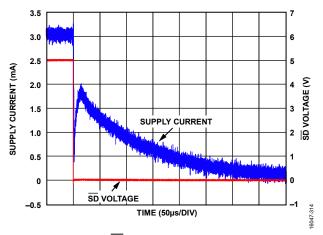

The ADHV4702-1 is equipped with a power saving shutdown feature. When the  $\overline{SD}$  pin voltage is brought low to within 0.8 V of DGND, the amplifier is disabled and put in a low power state, reducing its quiescent current to approximately 0.18 mA. The  $\overline{SD}$  pin has an internal approximately 400 k $\Omega$  pull-up resistor that enables the amplifier if  $\overline{SD}$  is left floating. When turning the amplifier on from the shutdown state, pull the  $\overline{SD}$  pin high to at least 1.6 V above the DGND pin. The  $\overline{SD}$  pin response time for starting up and coming out of shutdown is shown in Figure 53 and Figure 54. The  $\overline{SD}$  pin can support digital logic levels down to 2.5 V. The  $\overline{SD}$  pin can be used to implement thermal shutdown and short-circuit protection when used in conjunction with the temperature monitor feature of the ADHV4702-1.

Figure 53. SD Pin Response Time, Turning On

Figure 54. SD Pin Response Time, Turning Off

#### **TEMPERATURE MONITOR (TMP)**

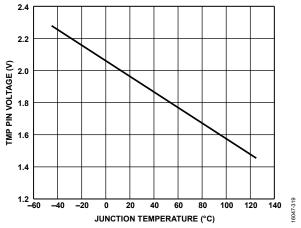

The ADHV4702-1 features an on-chip temperature sensor in close proximity to the output stage, where die temperature is the highest. The output voltage of the temperature sensor appears at the TMP pin. As an approximate indicator of die temperature, TMP voltage can be used to monitor power dissipation and implement thermal shutdown. The TMP voltage at room temperature is nominally 1.9 V, changing at approximately –4.5 mV/°C, as shown in Figure 55. More precise temperature readings can be achieved through a one-time room temperature calibration of the TMP pin.

Figure 55. TMP Pin Voltage vs. Junction Temperature

#### **OVERTEMPERATURE PROTECTION**

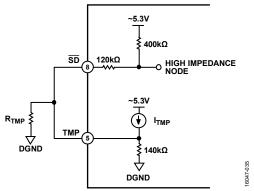

Operation at or beyond the operating temperature specified in the Absolute Maximum Ratings section can affect product reliability. To minimize this risk, the ADHV4702-1 features an optional, resistor programmable thermal shutdown where the TMP pin voltage asserts the  $\overline{SD}$  pin. In addition to proper heat sinking, thermal shutdown is recommended to protect the amplifier from an overtemperature condition. To implement the thermal shutdown function, tie TMP to  $\overline{SD}$ , as shown in Figure 56, and connect a 200 k $\Omega$  resistor (R<sub>TMP</sub>) from TMP and  $\overline{SD}$  to DGND in close proximity to the ADHV4702-1.

Device to device variation in the TMP pin voltage may result in different shutdown threshold temperatures or shutdown response times among various devices while implementing the 200 k $\Omega$  R<sub>TMP</sub>. The shutdown threshold can be adjusted with a smaller R<sub>TMP</sub> resistance, yielding a lower threshold temperature.

The  $R_{TMP}$  together with the internal resistors of TMP form a voltage divider that influences the TMP pin reading and TMP voltage drift. The TMP data in Table 1 and the Temperature Monitor (TMP) section is only valid when  $R_{TMP}$  is uninstalled.

Figure 56. TMP and SD Pin Configuration for Short-Circuit Protection and Thermal Shutdown

## OUTPUT CURRENT DRIVE AND SHORT-CIRCUIT PROTECTION

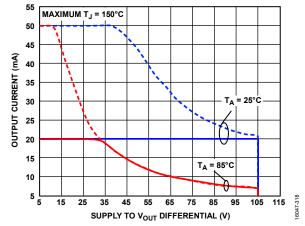

The ADHV4702-1 uses an output stage constructed with cascaded, double diffused, metal-oxide-semiconductor (DMOS) high voltage transistors that provide wide output swing. The ADHV4702-1 can typically drive a 20 mA load current continuously. Though with proper thermal management, the ADHV4702-1 can deliver up to 50 mA. Short-circuit protection is provided by means of the thermal shutdown feature. To enable short-circuit protection, connect the  $\overline{\text{SD}}$  and TMP pins, and tie both to DGND with a 200 k $\Omega$   $R_{\text{TMP}}$ .

## EXTERNAL COMPENSATION AND CAPACITIVE LOAD ( $C_{LOAD}$ ) DRIVING

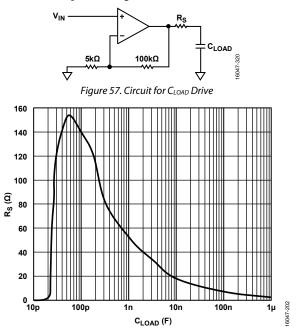

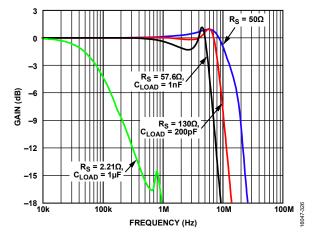

When driving a  $C_{LOAD}$ , the amplifier output resistance and the load capacitance form a pole in the transfer function of the amplifier. This additional pole reduces phase margin at higher frequencies and, if left uncompensated, can result in excessive peaking and instability. Placing a series resistor (Rs) between the amplifier output and  $C_{LOAD}$  (as shown in Figure 57) allows the ADHV4702-1 to drive capacitive loads beyond 1  $\mu$ F. Figure 58 shows the series resistor value vs. load capacitance for a maximum of 2 dB peaking in the circuit of Figure 57.

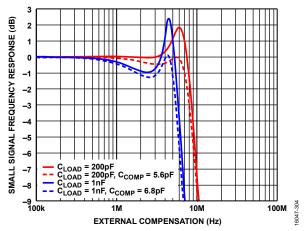

In addition to the series resistor, the ADHV4702-1 includes an optional external compensation feature for driving capacitive loads. A capacitor ( $C_{\text{COMP}}$ ) can be installed between COMP and OUT to reduce output stage peaking associated with capacitive loads.  $C_{\text{COMP}}$  must be rated for the full supply differential. Figure 60 shows the effect of  $C_{\text{COMP}}$  on various capacitive loads.

The values shown in Figure 58, Figure 59, and Figure 60 are for unity gain configuration with a purely  $C_{\text{LOAD}}$ . This is a worst case scenario because the amplifier is more stable at higher gains and with some resistive load in parallel with the load capacitance. Although the  $R_{\text{S}}$  or  $C_{\text{COMP}}$  significantly increases the stability while driving  $C_{\text{LOAD}}$ , they also reduce the headroom and bandwidth while driving a resistive load. For resistive loads, leave the COMP pin floating.

Figure 58.  $R_S$  vs.  $C_{LOAD}$  for Maximum 2 dB Peaking for Circuit from Figure 57,  $T_A = 25^{\circ}\text{C}$ ,  $A_V = 1$ ,  $V_S = \pm 110$  V,  $V_{OUT} = 100$  mV p-p,  $R_F = 0$   $\Omega$ ,  $R_{ADJ} = 0$   $\Omega$

Figure 59. Small Signal Response for Various  $C_{LOAD}$  and  $R_S$  Values,  $T_A=25$  °C,  $A_V=1$ ,  $V_S=\pm 110$  V,  $V_{OUT}=100$  mV p-p,  $R_F=0$   $\Omega$ ,  $R_{ADJ}=0$   $\Omega$

Figure 60. Small Signal Frequency Response vs. External Compensation,  $T_A = 25^{\circ}\text{C}$ ,  $A_V = 1$ ,  $V_S = \pm 110 \text{ V}$ ,  $V_{OUT} = 100 \text{ mV}$  p-p,  $R_F = 0 \Omega$ ,  $R_{ADJ} = 0 \Omega$

#### **SAFE OPERATING AREA**

The SOA represents the power handling capability of the device under various conditions.

The power dissipation of the ADHV4702-1 occurs primarily from the slew boosting circuit and output stage. The slew boosting circuit requires additional supply current. Operating the amplifier at its maximum slew rate at larger swing or at a high frequency increases the current consumption of the slew boosting circuit, increasing the T<sub>J</sub>. Figure 61 shows the dynamic SOA that maintains a T<sub>J</sub> less than 150°C. The curve shows the maximum safe square wave frequency for a given amplitude. Operating the ADHV4702-1 outside of the boundaries can cause permanent damage. Using additional thermal management or input clamping diodes expands the dynamic SOA significantly. However, using input clamping diodes can compromise the slew rate and the large signal bandwidth.

The dc SOA is a curve of output current vs. the voltage across the output stage, which is the voltage difference between supply and output ( $V_S - V_{OUT}$ ) under which the amplifier can operate at a safe  $T_J$ . The areas under the curves of Figure 62 show the operational boundaries of the ADHV4702-1 that maintain a  $T_J \leq 150^{\circ}\text{C}$ .

The SOA curves are unique to the conditions under which they were developed, such as PCB, heat sink, and  $T_A$ . All testing was performed in a still air environment. Forced air convection in any of the test cases effectively lowers  $\theta_{JA}$  and expands the SOA.

Figure 61. Dynamic SOA at  $T_A$  = 25°C and  $T_A$  = 85°C With and Without Input Clamping Diodes,  $A_V$  = 20,  $V_S$  =  $\pm 110$  V,  $R_F$  = 100 k $\Omega$ ,  $R_{LOAD}$  = 10 k $\Omega$ ,  $R_{ADJ}$  = 0  $\Omega$

Figure 62. DC SOA at  $T_A = 25^{\circ}$ C and  $T_A = 85^{\circ}$ C,  $A_V = 20$ ,  $V_S = \pm 110$  V,  $R_F = 100$  kO.  $R_{ADI} = 0$  O

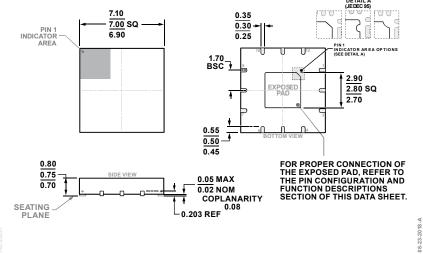

## LFCSP PACKAGE AND HIGH VOLTAGE PIN SPACING

A 7 mm  $\times$  7 mm, 12-lead LFCSP with EPAD was selected for the ADHV4702-1 to provide high reliability and compliance to regional and global high voltage standards regarding dielectric withstanding (clearance) and carbonization of package surface (creepage). The package dimensions are shown in Figure 66. The ADHV4702-1 meets the minimum 1.25 mm spacing requirement of IEC Standard 61010-1 for creepage distance to preclude failure due to carbon tracking at 250 V rms. To maintain these protections, it is essential to remove all flux and soldering residue around the package pins and exposed pad. Refer to the IEC 61010-1 standard for additional information.

#### **EXPOSED PAD (EPAD)**

The copper EPAD of the LFCSP provides a thermally conductive path to the PCB, which can be attached to a heat sink to improve heat dissipation. There is no internal electrical connection to the EPAD. High voltage isolation allows the EPAD to be safely biased to a 0 V ground plane, regardless of VCC or VEE voltages.

# APPLICATIONS INFORMATION POWER SUPPLY AND DECOUPLING

The ADHV4702-1 can operate from a single supply or dual supply. The total supply voltage (VCC – VEE) must be between 24 V and 220 V. The ADHV4702-1 requires a minimum supply voltage of  $\pm 12$  V from the reference voltage for normal operation. Decouple each supply pin to ground using high quality, low effective series resistance (ESR), 0.1  $\mu F$  capacitors. Place decoupling capacitors as close to the supply pins as possible. Additionally, place 1.2  $\mu F$  tantalum capacitors from each supply to ground to provide sufficient low frequency decoupling and supply the needed current to support large, fast slewing signals at the ADHV4702-1 output. To ensure reliable operation under high voltages, the voltage ratings for the bypass capacitors must be higher than the supply voltages of the ADHV4702-1.

#### **HIGH VOLTAGE GUARD RING**

The ADHV4702-1 features a pin placement that facilitates the use of a guard ring around the noninverting input of the amplifier. Guarding minimizes leakage from nearby pins and helps to achieve the benefit of low input bias current. The guard must be free of solder mask so that it remains exposed on the surface of the PCB. Drive the guard ring to a potential that tracks the input of the amplifier.

#### HIGH VOLTAGE DAC VOLTAGE SUBTRACTOR

The ADHV4702-1 can be combined with a dual, 16-bit voltage output, DAC, such as the AD5752R, to produce a versatile high voltage DAC solution. For this configuration, set up the ADHV4702-1 as a voltage subtractor with a gain of 20, which is ideally suited for chemical analysis (mass spectrometry), piezodrive, scanning electron microscope (SEM), LiDAR APD/SPAD, and silicon photomultiplier bias control applications.

Figure 63. ADHV4702-1 Configured as a Voltage Subtractor Using DACs

#### **HIGH CURRENT OUTPUT DRIVER**

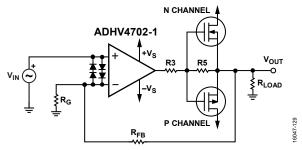

Figure 64 shows a system level application of the ADHV4702-1 that boosts the output current drive of the amplifier. By introducing a discrete unity-gain output stage, the ADHV4702-1 can be used as a high power output driver retaining the precision performance capabilities of the standalone amplifier, such as offset, drift, open-loop gain, and CMRR, while increasing the output current drive up to the current handling capabilities of the discrete devices.

Figure 64. High Current Output Driver Schematic

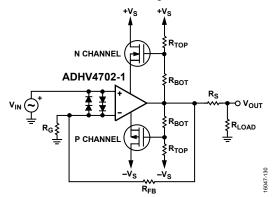

#### SIGNAL RANGE EXTENDER

Figure 65 shows an example of a signal range extender configuration. By introducing two additional high power, discrete, metal-oxide semiconductor field effect transistors (MOSFETs), the range extender can deliver at least twice the signal range (depending on the MOSFET selection), while retaining the original performance characteristics of the amplifier.

Figure 65. Voltage Extender Schematic

### **OUTLINE DIMENSIONS**

Figure 66. 12-Lead Lead Frame Chip Scale Package [LFCSP] 7 mm × 7 mm Body and 0.75 mm Package Height (CP-12-8) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                           | Package Option |

|--------------------|-------------------|-----------------------------------------------|----------------|

| ADHV4702-1BCPZ     | −40°C to +85°C    | 12-Lead Lead Frame Chip Scale Package [LFCSP] | CP-12-8        |

| ADHV4702-1BCPZ-R7  | −40°C to +85°C    | 12-Lead Lead Frame Chip Scale Package [LFCSP] | CP-12-8        |

| EVAL-ADHV4702-1CPZ |                   | Evaluation Board                              |                |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.